Regular eXpression Processor IP

Filter

Compare

39

IP

from

22

vendors

(1

-

10)

-

EdDSA Curve25519 signature generation engine

- The EdDSA Curve25519 extension adds hardware support for modern elliptic-curve cryptography inside DCD-SEMI’s configurable cryptographic co-processor.

- The implementation is based on Curve25519, a widely adopted 255-bit elliptic curve designed for efficient key exchange and digital signatures, with strong resistance to side-channel attacks and high performance in constrained embedded environments.

-

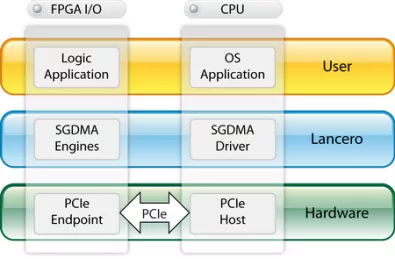

Lancero Scatter-Gather DMA Engine for PCI Express

- PCIe I/O performance: 200 MB/s x1 Gen 1 up to 3360 MB/s x8 Gen 2

- Easily connect logic and high-speed I/O peripherals to PCI Express

- Target Bridge supports Avalon Memory Mapped custom logic

- SGDMA Engine supports Avalon Streaming burst access devices

-

Flash Memory LDPC Decoder IP Core

- Quasi cyclic (QC) – Algebraic constructed – LDPC Code

- Regular Parity Check Matrix

- Codeword length: 16 K

- Code rate 0.953

- No or very low error floor

- Parallel/Layered decoding

-

-

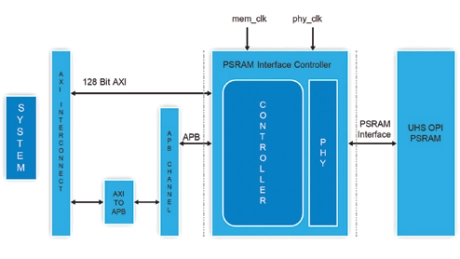

AP Memory UHS PSRAM Controller

- This controller supports AP Memory’s UHS series of high speed PSRAM devices which can clock frequencies of upto 1066 MHz.

- This controller enables smooth integration of APMemory’s UHS OPI PSRAM memory device chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

Standalone stateful hash-based signatures software library

- The SHSlib is a standalone stateful hash-based signatures software library, which provides signature verification for stateful hash-based signatures.

- SHSlib implements SHA-256 operation in software and has hardware integration with the EIP-120. In addition, it can be integrated with another hardware SHA core for acceleration.

-

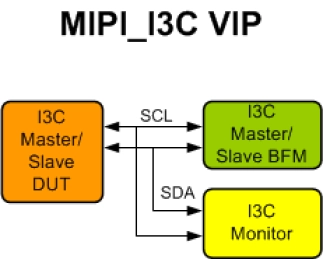

MIPI I3C Verification IP

- Compliant with MIPI I3C version 1.1 specification.

- Full MIPI I3C Master and Slave functionality

- Two wire serial interface up to 12.5 MHz

- Supports all MIPI I3C Device Types.

-

Smart Network-on-Chip (NoC) IP

- Smart NoC automation

- Topology generation with minimum wire length

- Scripting-driven regular topology creation

- Incremental design capability

- Auto-timing closure assist

-

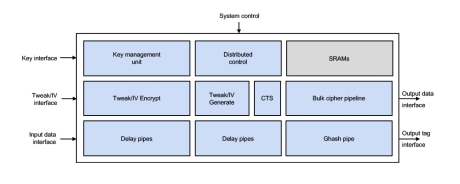

High-speed Inline Cipher Engine

- The ICE-IP-338 data path can be scaled to widths that are multiples of 128 bit to allow a tradeoff between area and performance that best fits the target application.

- Configuration options include or exclude support for CipherText Stealing (CTS), the GCM mode, and the SM4 algorithm and/or Datapath Integrity logic.

- The cryptographic AES and SM4 primitives can be provided with or without side channel attack DPA countermeasures.

-

JPEG XS compression IP core for HD - Max fps: 480 - Color sampling: 4:2:2 / 4:0:0

- Max res: 4096x2160

- Max fps: 480

- Color sampling: 4:2:2 / 4:0:0

- Bit depth: 8, 10, 12

- Minimum frequency (internal core clock): 300 MHz