PowerPC IP

Filter

Compare

31

IP

from

7

vendors

(1

-

10)

-

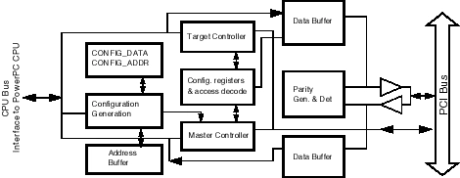

PowerPC to PCI Bridge

- Fully supports PCI specification 2.1 and 2.2 protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Supports all PowerPC CPU with 603 bus interface and MPC860 interface.

-

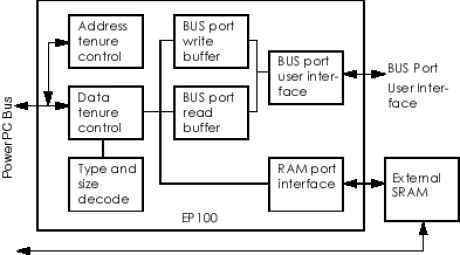

PowerPC Bus Slave

- Fully supports PowerPC 60x bus protocol including PowerPC 603, 604, 740, 750 and MPC8260.

- Designed for ASIC or PLD implementations in various system environ-ments.

- Fully static design with edge triggered flip-flops.

- Direct support for standard asynchronous SRAM and synchronous BURST SRAM.

-

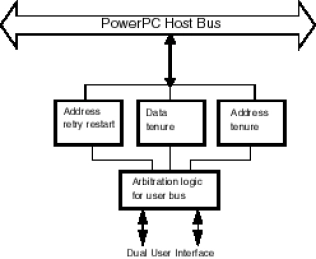

PowerPC Bus Master

- Fully supports PowerPC 60x bus protocol, include PowerPC 603, 604, 740, 750 and 8260.

- Designed for ASIC or PLD implementations in various system environments.

- Fully static design with edge triggered flip-flops.

- Automatic bus arbitration for address bus and data bus based on internal bus request.

-

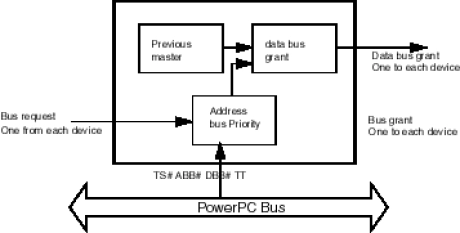

PowerPC Bus Arbiter

- Fully supports PowerPC 60x bus protocol, include PowerPC 603, 604, 740, 750 and 8260.

- Designed for ASIC or PLD implementations in various system environments.

- Fully static design with edge triggered flip-flops.

- Supports up to eight PowerPC bus masters with unlimited slave device support.

-

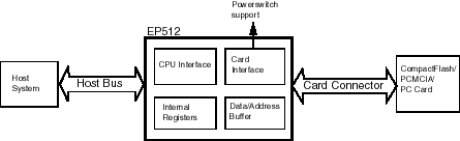

CompactFlash/PCMCIA Host Controller with EXCA Registers

- Compliant with PC Card Standard 8.0, PCMCIA 2.1/JIEDA 4.2 and CompactFlash 1.4.

- Allows host CPU to access CompactFlash, PC Card/PCMCIA devices.

- 82365SL-compatible register set, EXCA compatible.

-

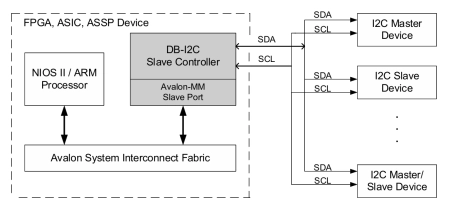

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

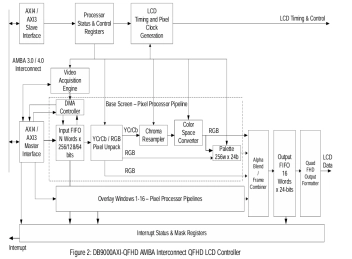

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

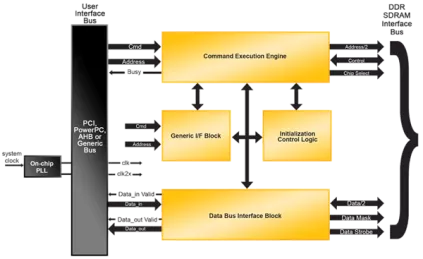

DDR SDRAM Controller - Pipelined for ispXPGA and ORCA4

- Performance of Greater than 100MHz (200 DDR)

- Interfaces to JEDEC Standard DDR SDRAMs

- Supports DDR SDRAM Data Widths of 16, 32 and 64 Bits

- Supports up to 8 External Memory Banks

-

Advanced 2D Graphics Controller

- Fully synchronous, synthesizable and technology independent RTL code

- Capable of drawing shapes such as pixels, lines and rectangles

-

I2C Controller IP – Slave, Parameterized FIFO, AHB Bus

-

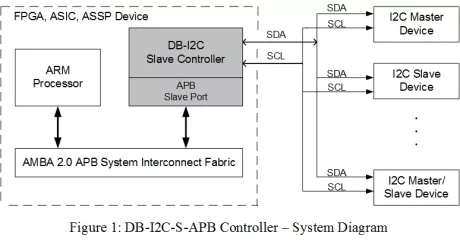

The DB-I2C-S-AHB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0/3.0 AHB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-AHB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB I2C-S-AHB Controller IP Core embedded within an integrated circuit device.

-