PCIe 5.0 Serdes PHY IP

Filter

Compare

29

IP

from

7

vendors

(1

-

10)

-

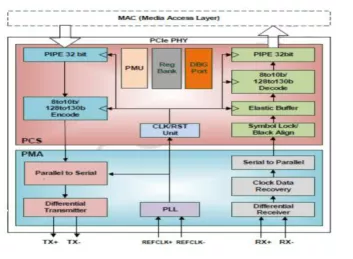

PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 5.0 Base Specification

- Compliant with PIPE 5.1

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s, 16.0 GT/s and 32GT/s

- Supported physical lane width: x4

-

PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Compliant with PCIe 5.0 Base Specification

- Compliant with PIPE 5.1

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s, 16.0 GT/s and 32GT/s

- Supported physical lane width: x4

-

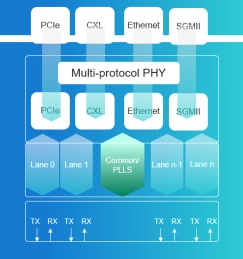

PHY for PCIe 5.0 and CXL for TSMC 7nm FinFet

- High-performance PHY for data center applications

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Multi-protocol support for application flexibility

-

PHY for PCIe 5.0 and CXL

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Advanced equalization and clock-data-recovery to deliver unmatched channel loss handling performance and reliability

- Eye Surf —provides convenient access to an integrated non-destructive real-time eye scope and BER bathtub curve to monitor the bit error rate (BER) and the link performance during live traffic

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in SMIC 40LP

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 22ULP

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 3.0 Serdes PHY IP, Silicon Proven in TSMC 7nm

- Compliant with PCIe 3.0 Base Specification

- Compliant with PIPE 4.3

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s and 8.0 GT/s

- Supported physical lane width: x4

-

PCIe 4.0 Serdes PHY IP, Silicon Proven in TSMC 16FFC

- Compliant with PCIe 4.0 Base Specification

- Compliant with PIPE 4.4

- Supported data transfer rate: 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s

- Supported physical lane width: x4