PCI-X IP

Filter

Compare

14

IP

from

5

vendors

(1

-

10)

-

64-bit Initiator/Target for PCI-X & 32- and 64-bit Initiator/Target for PCI

- Fully PCI-X 2.0 Mode1 compliant core, 64-bit, 133/66MHz interface with 3.3 V operation

- Customizable, programmable, single-chip solution

- Predefined implementation for predictable timing

- Incorporates Xilinx Smart-IP™ Technology

-

64-bit Initiator/Target for PCI-X & 32- and 64-bit Initiator/Target for PCI

- Fully PCI-X 2.0 Mode1 compliant core, 64-bit, 133/66MHz interface with 3.3 V operation

- Customizable, programmable, single-chip solution

- Predefined implementation for predictable timing

- Incorporates Xilinx Smart-IP™ Technology

-

64-bit Initiator/Target for PCI-X & 32- and 64-bit Initiator/Target for PCI

- Fully PCI-X 2.0 Mode1 compliant core, 64-bit, 133/66MHz interface with 3.3 V operation

- Customizable, programmable, single-chip solution

- Predefined implementation for predictable timing

- Incorporates Xilinx Smart-IP™ Technology

-

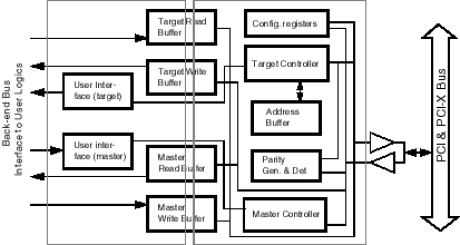

64-bit PCI-X Master/Target

- Fully supports PCI and PCI-X protocol.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Efficient user interface for different types of user devices.

-

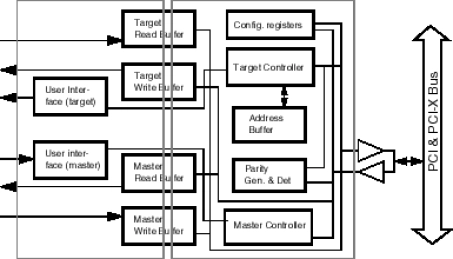

64-bit PCI-X Host Bridge

- Fully supports PCI 2.3 and PCI-X protocol 1.0b.

- Designed for ASIC and PLD implementations.

- Fully static design with edge triggered flip-flops.

- Efficient user interface for different types of user devices.

-

SMIC 0.18um PCI-X IO

- SMIC 0.18um process

- Non-inverter bi-direction pad

- Compatible to PCI-X Addendum Revision 1.0 Released at SEP 22,1999

- Level shift are built in