PCI Express Switch IP

Filter

Compare

114

IP

from

11

vendors

(1

-

10)

-

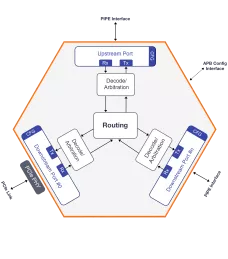

Multi-Port Switch IP for PCI Express

- Designed according to the PCI Express 4.0, 3.1, 2.1, and 1.1 specifications, including the latest errata

- Designed according to the PCI-SIG Single-Root I/O Virtualization specification

- Supports PIPE PHY interface definition including variable clock and variable data

- Supports 16.0, 8.0, 5.0 and 2.5 Gbps line rates

-

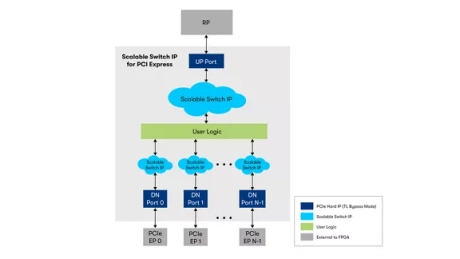

Scalable Switch Intel® FPGA IP for PCI Express

- The Scalable Switch Intel® FPGA IP for PCI Express is a fully configurable switch that implements one fully configurable upstream port and connectivity for up to 64 downstream ports.

-

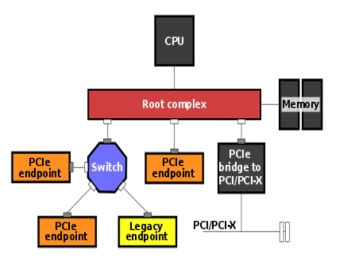

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

PCI Express to AMBA 4 AXI/3 AXI Bridge

- Complete IP solution consists of digital controllers, PHYs and verification IP

- Fully supports the Synopsys Controller IP for PCI Express Endpoint, Root Port, Dual Mode (EP/RP), and Switch port types

- Fully compliant with the AMBA 3 AXI and 4 AXI interconnects

- Full protocol mapping from PCI Express to the AMBA 3 AXI or 4 AXI bus protocol

-

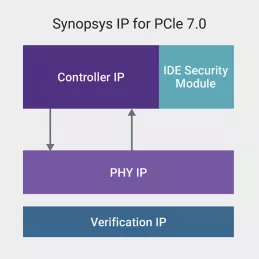

Controller IP for PCI Express 7.0

- Supports all required features of the PCI Express 7.0 (128 GT/s) specification

- Allows a full 128GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Advanced RAS-DES features for simplified bring-up and debug

-

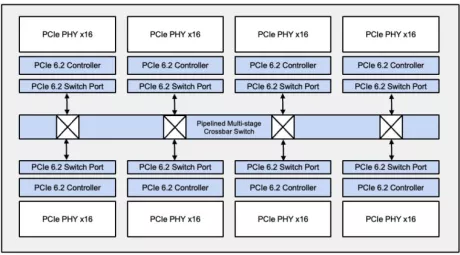

PCIe 6.2 Switch

- 1 upstream port, up to 7 downstream ports

- Up to 128 lanes

- PCIe TLP routing: Configuration, Memory Write/Read, I/O and Messages Packets

- L1 and wake-up events forwarding

-

Configurable CCIX controllers for CCIX 32G supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Supports all required features of the CCIX 1.1 specification, including 32GT/s, and ESM support for 25GT/s and 20GT/s

- Supports all required features of the PCI Express 5.0, 4.0, 3.1, 2.1 and 1.1 specifications

- Supports up to sixteen 32.0 25.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 128-, 256- or 512-bit datapath widths for maximum flexibility

-

Automotive-grade controllers for PCIe 2.0/1.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 6.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

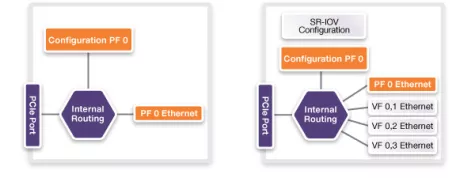

PCIe Switch for USB4

- Fully transparent design eliminates the need for Host configuration and management software

- Built-in support for PIPE-attached embedded endpoints (including 64-bit PIPE) for reduced BoM, latency, and power

- Seamless implementation on ASIC and FPGA with same RTL code base, up to x8 Gen4 per port on FPGA (or x16 Gen3)

- Lowest latency switching logic on the market (2 clock cycles)