PCI Express DMA IP

Filter

Compare

38

IP

from

11

vendors

(1

-

10)

-

DMA for PCI Express (PCIe) Subsystem

- DMA for PCI Express Subsystem connects to the PCI Express Integrated Block. Both IPs are required to build the PCI Express DMA solution

- Support for 64, 128, 256, 512-bit datapath for UltraScale+™, UltraScale™ devices. Support for 64 and 128-bit datapath for Virtex®-7 XT devices

- Up to 4 host-to-card (H2C/Read) data channels for UltraScale+, UltraScale devices. Up to 2 such channels for Virtex-7 XT devices

- Up to 4 card-to-host (C2H/Write) data channels for UltraScale+, UltraScale devices. Up to 2 such channels for Virtex-7 XT devices

-

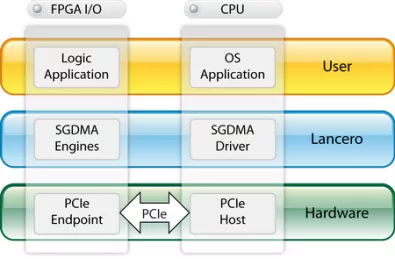

Lancero Scatter-Gather DMA Engine for PCI Express

- PCIe I/O performance: 200 MB/s x1 Gen 1 up to 3360 MB/s x8 Gen 2

- Easily connect logic and high-speed I/O peripherals to PCI Express

- Target Bridge supports Avalon Memory Mapped custom logic

- SGDMA Engine supports Avalon Streaming burst access devices

-

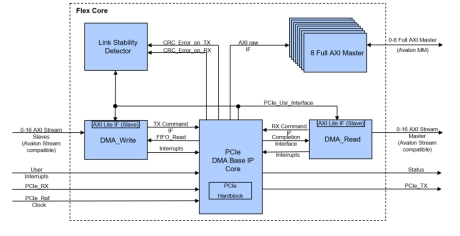

Multi-Channel Flex DMA IP Core for PCI Express

- The Multi-Channel DMA IP Core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- Up to 16 independent AXI Stream Slaves write DMA Data to the Host. Up to 16 AXI Stream Masters read DMA Data from the Host and present it to the User Logic.

- Each channel operates on a separate memory area. Additional 8 AXI4 Masters are available to interface full AXI or AXI-Lite peripherals with the Host.

-

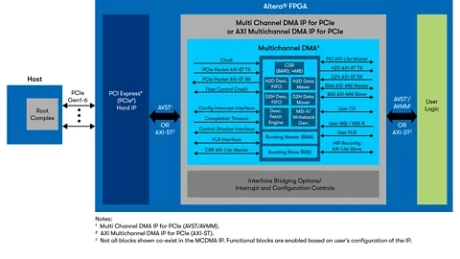

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

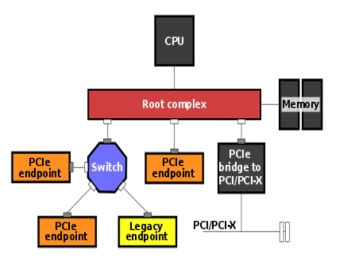

PCIe - PCI Express Controller

- The PCIe 3.0 (Peripheral Component Interconnect Express 3.0) is a computer hardware interface standard that is used to connect various components to a computer's motherboard.

- It is the third generation of the PCIe standard and offers increased bandwidth, improved performance, and reduced power consumption compared to its predecessor, PCIe 2.0 Overall, PCIe 3.0 provides faster and more efficient communication between the various components in a computer, including graphics cards, network adapters, and storage devices, resulting in better overall performance.

-

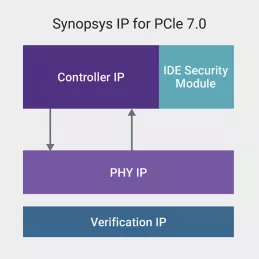

Controller IP for PCI Express 7.0

- Supports all required features of the PCI Express 7.0 (128 GT/s) specification

- Allows a full 128GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

- Advanced RAS-DES features for simplified bring-up and debug

-

QDMA Subsystem for PCI Express

- Supports 64, 128, 256 and 512-bit data path

- Supports x1, x2, x4, x8, or x16 link widths.

- Supports Gen1, Gen2, and Gen3 link speeds

- Support for both the AXI4-Memory Mapped and AXI4-Stream interfaces per queue

-

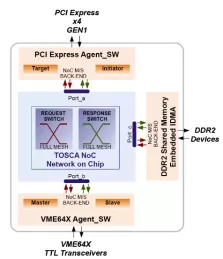

PCI Express to VME64x Transparent Bridge

- Complete PCI Express to VME64x Master/Slave Bridge

- Improved performance compared to currently available ASIC solutions

- PCI Express x4 GEN1/2

- VME64x supported modes: SLT, BLT, MBLT, 2eVME and 2eSST

-

Virtex-7 FPGA Gen3 Integrated Block for PCI Express (PCIe)

- Compliant with the PCI Express Base Specification 3.0

- Supported Lane width: x1, x2, x4 and x8

- Fully compliant with PCI Express transaction ordering rules

- Optimal buffering for high bandwidth Direct Memory Access (DMA) applications

-

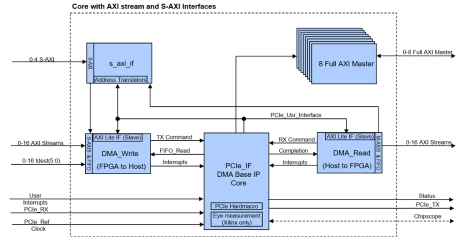

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.