MPEG-H Audio IP

Filter

Compare

15

IP

from

11

vendors

(1

-

10)

-

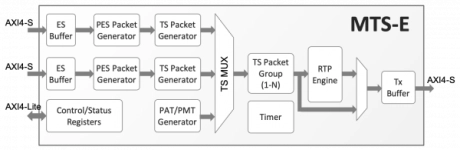

MPEG Transport Stream Multiplexing & Encapsulation Engine

- The MTS-E core multiplexes and encapsulates audio, video, and metadata streams in a single MPEG Transport Stream (MTS), and optionally encapsulates the TS packets in Real-Time Transport Protocol (RTP) packets.

- Under its default configuration, the MTS-E multiplexing and encapsulation engine supports two input stream channels, e.g., one Audio and one Video.

-

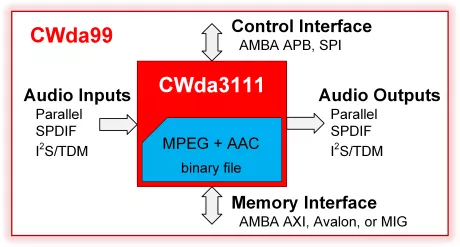

MPEG-1/2 + AAC Audio Decoder

- The MPEG-1/2+AAC Audio Decoder (CWda99) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the MPEG + AAC decoder software and the Coreworks processor based hardware audio engine platform (CWda3111).

-

MPEG-2 Transport Stream Encapsulation for SMPTE2022

- Brings full interoperability with VSF recommendations to carry SDI over SMPTE2022-1/2 using JPEG 2000 Broadcast profile in MPEG-2 TS over IP

-

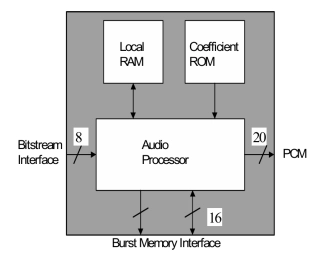

Dolby Digital/AC-3/MPEG Audio Decoding Core

- The J1 is a core cell design of an application specific signal processor which performs both Dolby Digital/AC-3 and MPEG audio decompression in a single design.

- The J1 is capable of decoding all AC-3 bitstreams with full support for bitstreams encoded with 5.1 channels and data rates of up to 640kb/s.

- The J1 downmixing capability produces stereo output in either normal or Pro-Logic compatible modes, making it ideal for DVD and set-top applications.

-

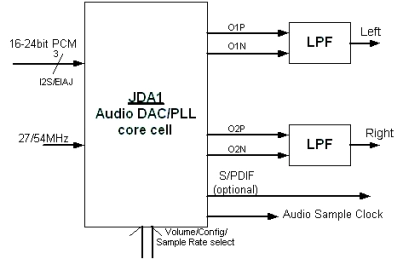

Multi-rate Audio 24-Bit DAC/PLL Core

- Operates from single 27/54MHz clock.

- Ideal for MPEG, AC-3, DVD systems

- Internally generates audio sample clocks

- Multi-sample rates: 32, 44.1, 48 KHz

-

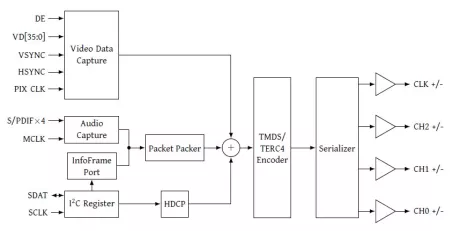

HDMI 2.0 Transmitter

- Compliant with HDMI 2.0 specification and HDCP 1.4 Specification compliant

- Supports high-definition video with up to 4K resolution

- Support for up to 48-bit Deep Color

- Supports industry-standard S/PDIF for digital audio using IEC 60958 2-channel PCM, and compressed (encoded) audio data (DTS, AC3, MPEG Audio) using IEC 61937 format

-

DAB modulator

- Fully compliant with ETSI EN 300 401 V1.4.1 2006-06, for DAB

- DAB-Modes: I, II, III, IV

- All protection levels supported

- Synchronous design

-

H.265/HEVC 422 10bit Decoder for 4K

- Video stream

- - Compliant with ITU-T H.265, ISO/IEC 23008-2

- - Main / Main 12 Profile Level 1 to 6.1

- - Input format: Annex. B

-

H.265/HEVC 422 10bit Encoder for 4K

- Compliant with ITU-T H.265, ISO/IEC 23008-2

- Main / Main 12 Profile Level 1 to 6.1

- Input format: Annex. B

-

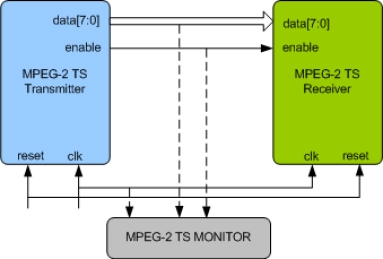

MPEG2TS Verification IP

- Full MPEG-2 TS Transmitter and Receiver functionality.

- Supports the combination of the video and audio coding methods defined in Parts 2 and 3 of ISO/IEC 13818

- Supports Generic coding of moving pictures and associated audio information Part 7 Advanced Audio Coding (AAC).

- Supports Generic coding of moving pictures and associated audio information for Systems as per ISO/IEC 13818-1