MIPS CPU IP

Filter

Compare

19

IP

from

7

vendors

(1

-

10)

-

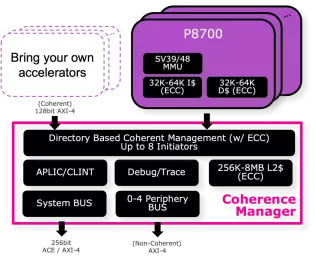

Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

- The only Multi-Threaded Out-of-Order RISC-V Core with ASIL-B Certification

- Highly scalable multi-core, multi-cluster, coherent computing solution

- MIPS extensions for improved performance and functionality

- Use in Automotive, Datacenter, and Embedded applications

-

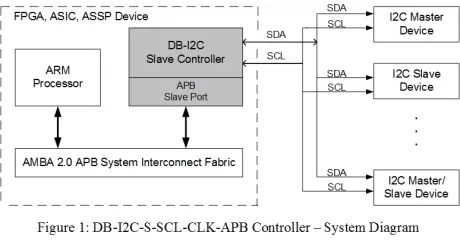

I2C Controller IP – Slave, SCL Clock, Parameterized FIFO, APB Bus. For low power requirements in I2C Slave Controller interface to CPU

-

The DB-I2C-S-SCL-CLK-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-SCL-CLK-APB, in the I2C Slave Controller Core managing the I2C protocol & physical layer, contains no free running clock, while interfacing through dual clock FIFOs to the AMBA APB Bus, for a low power, low noise Microprocessor interface to the I2C Bus. The I2C Slave Controller Core runs off the external SCL clock while the APB side off the APB Clock.

-

-

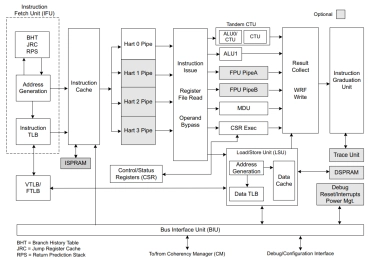

Data Movement Engine - Efficient data-processing and simultaneous multi-threading, low latency and deterministic data access

- Efficient throughput with the first RISC-V core to support up to 4-way multithreading

- Highly scalable multi-core, multi-cluster coherent computing solution

- MIPS Enhancements for increased connectivity and throughput

- Use in 5G/6G Comms Infrastructure, Automotive Gateways, Embedded & Datacenter

-

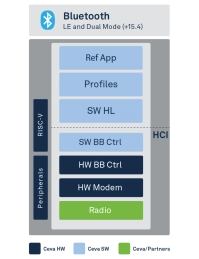

Bluetooth Connectivity Platform

- The Ceva-Waves Bluetooth platform comprises a comprehensive set of hardware IP, software modules, and radios from Ceva and third-party partners addressing a broad choice of processes and nodes, to implement highly efficient Bluetooth connectivity in SoCs.

- The latest Bluetooth standards, both Bluetooth LE and dual-mode versions are supported, and an available add-in extends support to IEEE 802.15.4.

-

Image Signal Processor IP enabling high performance real-time image processing

- Support DVP Input Interface

- Support 8-16 Bit Bayer RAW and ITU-R BT.601 & 656 Video Interface

- Test Pattern Generator (TPG)

- Black Level Measurement and Compensation (BLS)

- Sensor Linear Correction

-

USB 2.0 Digital Controller IP

- Fully supports Hi-Speed (480 Mbps), Full Speed (12 Mbps), and Low Speed (1.5 Mbps) (USB 2.0 Speeds) specifications

- Configurable root hub supports 1 to 15 downstream ports

- 60MHz or 30MHz input clock, and 48MHz and 12MHz input clocks

- ULPI and UTMI+ interfaces for rapid PHY integration

-

USB 1.1 Digital Controller IP

- Fully supports USB Full Speed and Low Speed (USB 1.1 Speeds)

- Configurable root hub supports 1 to 15 downstream ports

- Integrated DPLL simplifies transceiver integration

- Low gate counts, starting at 30k gates

-

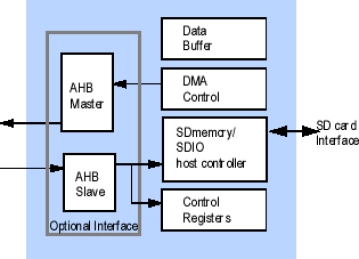

SD/SDIO 2.0 MMC Host Controller

- Host controller for SDIO, SD memory card, and MMC interface.

- Allows host CPU to access SD and MMC devices.

- Simple user interface optimized for on-chip bus connection.

- User interface supports 32-bit and 64-bit data.

-

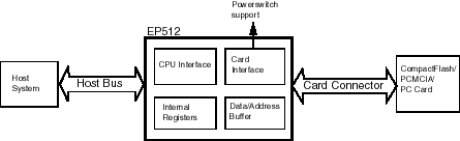

CompactFlash/PCMCIA Host Controller with EXCA Registers

- Compliant with PC Card Standard 8.0, PCMCIA 2.1/JIEDA 4.2 and CompactFlash 1.4.

- Allows host CPU to access CompactFlash, PC Card/PCMCIA devices.

- 82365SL-compatible register set, EXCA compatible.

-

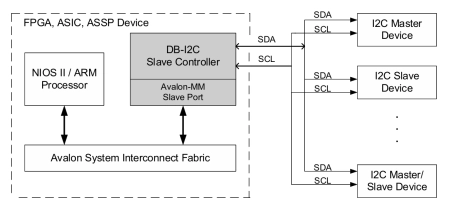

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.