LPDDR5X IP

Filter

Compare

68

IP

from

10

vendors

(1

-

10)

-

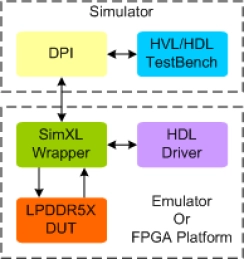

LPDDR5X Synthesizable Transactor

- Supports 100% of LPDDR5X protocol draft JEDEC specification and JESD209-5B specification.

- Supports all the LPDDR5X commands as per the specs.

- Supports device density up to 32GB.

- Supports X8 and X16 device modes.

-

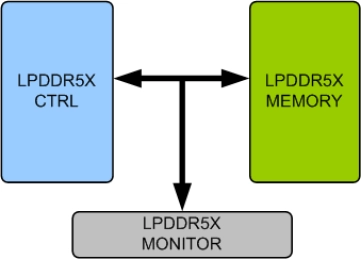

LPDDR5X Memory Model

- Supports LPDDR5X memory devices from all leading vendors.

- Supports 100% of LPDDR5X protocol draft JEDEC specification and JESD209-5B specification.

- Supports all the LPDDR5X commands as per the specs.

- Supports device density up to 32GB.

-

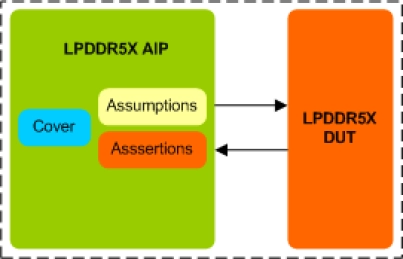

LPDDR5X Assertion IP

- Specification Compliance

- Supports 100% of LPDDR5X protocol draft JEDEC specification and JESD209-5B specification

- Supports all the LPDDR5X commands as per the specs

- Supports following device modes,

-

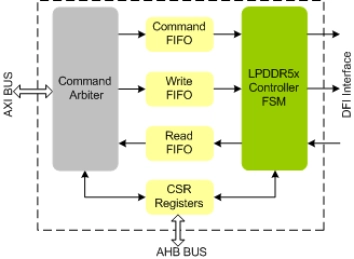

LPDDR5X Controller IIP

- Supports LPDDR5X protocol draft JEDEC Specification and JESD209-5B specification.

- Compliant with DFI version 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

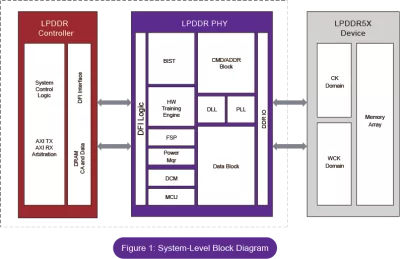

LPDDR5X PHY

- Compatible with JEDEC standards LPDDR4X , LPDDR5 and LPDDR5X SDRAMs

- Supports for data transfer rate up to 8533Mbps

- DFI 5.0 for PHY and controller interfaces

- Supports both firmware-based training and hardware-based training

-

LPDDR5X PHY

- Supports High Data Rate

- Compliant with JEDEC LPDDR5X standards

- Scalable Architecture: Supports multiple channels and ranks, offering flexibility for various memory configurations

- Supports all auto calibrations

- Supports High Data Rate

-

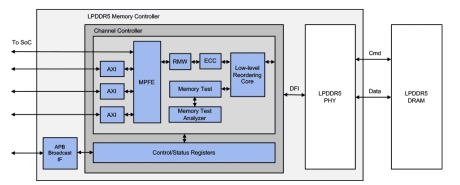

LPDDR Controller supporting LPDDR5X, LPDDR5, and LPDDR4X

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR Controller supporting LPDDR5X, LPDDR5 and LPDDR4X with Advanced Features Package

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR5T / LPDDR5X / LPDDR5 Controller

- Support for all LPDDR5T/5X/5 devices

- Bank management logic monitors status of each bank

- Queue-based user interface with reordering scheduler

- Look-ahead activate, precharge, and auto-precharge logic

- Parity protection for all stored control registers

- PHY interface based on DFI 5.1 standard

-

LPDDR Controller ASIL B Compliant supporting LPDDR5X, LPDDR5 and LPDDR4X for Automotive Applications

- Supports JEDEC standard LPDDR5X, LPDDR5 and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (AXI™4 / AXI™ 3) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5X/5/4X PHY and other LPDDR5X/5/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support