LPDDR4 memory IP

Filter

Compare

123

IP

from

15

vendors

(1

-

10)

-

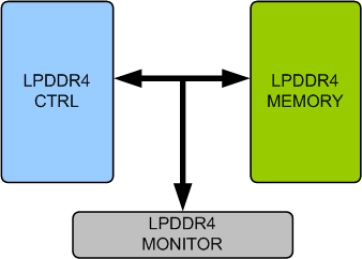

LPDDR4 Memory Model

- Supports LPDDR4 memory devices from all leading vendors.

- Supports 100% of LPDDR4 protocol standard JESD209-4, JESD209-4A, JESD209-4B, JESD209-4C, JESD209-4D, JESD209-4X and LPDDR4Y (Proposed).

- Supports all the LPDDR4 commands as per the specs.

- Supports up to 32 GB device density.

-

DDR3L/ LPDDR4/ DDR4 PHY IP - 1866Mbps (Silicon Proven in UMC 28HPC+)

- Supported DRAM type: DDR3L/DDR4/LPDDR4

- Maximum controller clock frequency of 400MHz resulting in maximum DRAM data rate of 1866Mbps

- Interface: SSTL135/POD12/LVSTL

- Data path width scales in 32-bit increment

-

DDR4 & LPDDR4 COMBO IO for memory controller PHY, 3200Mbps on TSMC 22nm

- The DDR4&LPDDR4 COMBO IO is used to transfer the Command/Address/Clk and Data between the memory controller PHY and the DRAM device

- The TX is designed to send information from PHY to DRAM and RX is designed to receive information which is from DRAM.

-

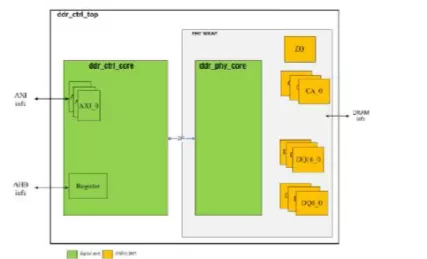

DDR4 / DDR3/ DDR3L / LPDDR4 Memory Controller IP optimized for low latency

- Support DDR3 / DDR3L / DDR4/ 3DS DDR4/ LPDDR4 / MRAM

- Support x8/x16/x32 DRAM data bus configuration (programmable)

- Support Multi-Ranks DRAM configuration

- DDR base on DFI spec 4.0 compliant.

-

Performance Enhanced version of DDR Enhanced Memory Ctl (uMCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

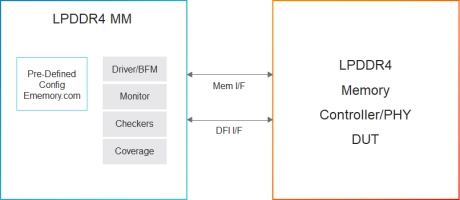

Simulation VIP for LPDDR4

- Speed (Mt/s)

- 2133MHz (4266MT/s)

- Device Density

- Supports a wide range of device densities from 4Gb to 32Gb

-

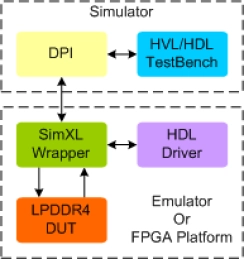

LPDDR4 Synthesizable Transactor

- Supports 100% of LPDDR4 protocol standard JESD209-4,JESD209-4A,JESD209-4B,JESD209-4C,JESD209-4D,JESD209-4X and JESD209-4Y (proposed)

- Supports all the LPDDR4 commands as per the specs

- Supports memory densities upto 32GB

- Supports device types X8 and X16

-

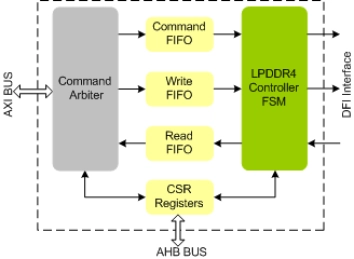

LPDDR4 Controller IIP

- Supports LPDDR4 protocol standard JESD209-4, JESD209-4A, JESD209-4B, JESD209-4C, JESD209-4X and JESD209-4Y (Proposed) Specification.

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

Performance Enhanced version of uMCTL2 supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3 and LPDDR2 for Automotive

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces

-

DDR Enhanced Protocol Controller (uPCTL2) supporting DDR4, DDR3, DDR2, LPDDR4, LPDDR3, and LPDDR2

- Select a complete multi-ported Enhanced Universal DDR Memory Controller offering 1 to 16 host ports, or join a third-party scheduler to a single-port Enhanced Universal Protocol Controller

- Support for JEDEC standard DDR2, DDR3, DDR4, LPDDR/Mobile DDR, LPDDR2, LPDDR3, and LPDDR4 SDRAMs

- Compatible with all Synopsys DDR PHYs (excluding DDR2/DDR PHYs) using DFI-compliant interfaces