LPDDR IP

Filter

Compare

353

IP

from

37

vendors

(1

-

10)

-

LPDDR Synthesizable Transactor

- Supports 100% of LPDDR protocol standard JESD209B and JESD209A-1

- Supports all the LPDDR commands as per the specs

- Supports up to 2GB device density

- Supports following devices:

-

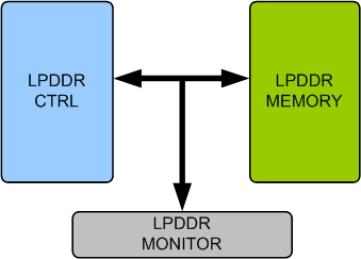

LPDDR Memory Model

- Supports LPDDR memory devices from all leading vendors.

- Supports 100% of LPDDR protocol standard JESD209B and JESD209A-1.

- Supports all the LPDDR commands as per the specs.

- Supports up to 2GB device density

-

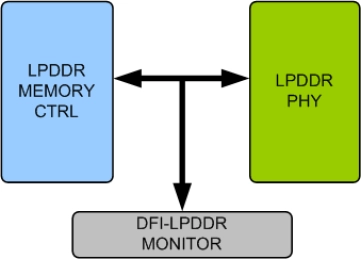

LPDDR DFI Verification IP

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf

- Supports all Interface Groups.

- Supports Write Transactions with Data mask

-

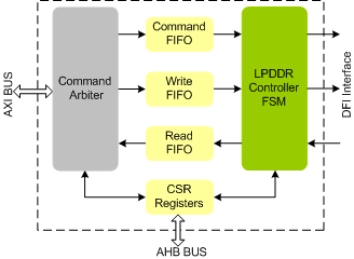

LPDDR Controller IIP

- Supports LPDDR protocol standard and JESD209A-1 and JESD209B Specification

- Compliant with DFI version 2.0 or higher Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transcations for AXI write and read channels

-

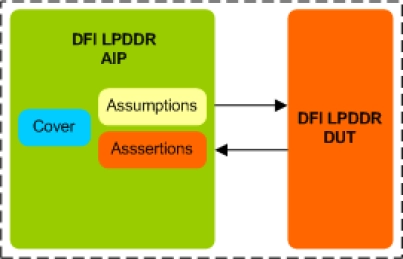

LPDDR DFI Assertion IP

- Specification Compliance

- Compliant with DFI version 2.0 or higher Specifications.

- Supports LPDDR devices compliant with JEDEC LPDDR SDRAM Standard JESD209A-1.pdf and JESD209B.pdf.

- Supports all Interface Groups.

-

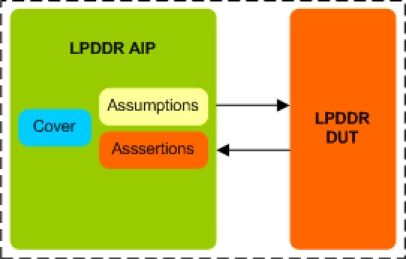

LPDDR Assertion IP

- Specification Compliance

- Supports all signal level checks including X detection

- Supports LPDDR memory devices from all leading vendors.

- Supports 100% of LPDDR protocol standard JESD209B and JESD209A-1.

-

LPDDR Controller

- Memory controller interface complies with DFI standard up to 5.0

- Application-optimized configurations for fast time to delivery and lower risk

- Sideband and in-line SEC/DED ECC

- Supports advanced RAS features including error scrubbing, parity, etc.

- Compliant to LPDDR5/4X/4/3 protocol memories

- Priority per command on Arm®AMBA® 4 AXI, AMBA 3 AXI

-

DDR and LPDDR Combo PHY

- Supports multiple combinations of DDR/LPDDR interfaces

- Compliant with JEDEC DDR and LPDDR standards

- Supports all auto calibrations

- Industry leading area and power

-

LPDDR Controller supporting LPDDR5, LPDDR4, and LPDDR4X

- Supports JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5/4/4X PHY and other LPDDR5/4/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support

-

LPDDR Controller supporting LPDDR5, LPDDR4 and LPDDR4X with Advanced Features Package

- Supports JEDEC standard LPDDR5, LPDDR4, and LPDDR4X SDRAMs

- Multiport Arm® AMBA® interface (4 AXI™/3 AXI™) with managed QoS or single-port host interface to the DDR controller

- DFI 5.0 compliant interface to Synopsys LPDDR5/4/4X PHY and other LPDDR5/4/4X PHYs

- Best-in-class performance with unique features such as QoS-based scheduling, inline ECC, and dual-channel support