IRIDA IP

Filter

Compare

9

IP

from

5

vendors

(1

-

9)

-

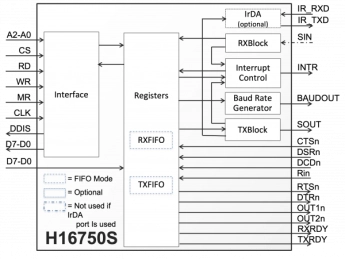

UART with FIFOs, IrDA and Synchronous CPU Interface

- Capable of running all existing 16450 and 16550a software

- Fully Synchronous design. All inputs and outputs are based on the rising edge of clock

- In FIFO mode, transmitter and receiver are each buffered with up to 256 byte FIFO’s to reduce the number of interrupts presented to the CPU

- Available with FIFO sizes of 8, 16, 32, 64, 128 or 256 bytes

-

IrDA Controller

- Rapid prototyping and time-to-market reduction

- Design risk elimination

- Development costs reduction

-

-

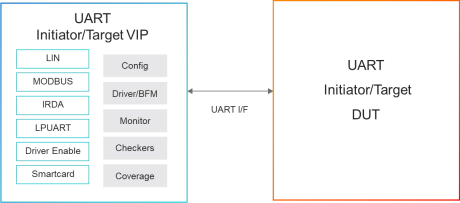

UART Verification IP

- Fully compatible with 16550.

- Transmit and receive commands allow the user to transmit and receive UART data.

- Support additional functionality of IRDA, RS232, RS422, RS485 and GPIO.

- Configurable baud rate.

-

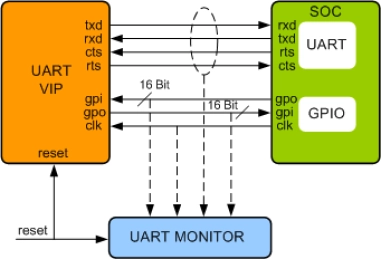

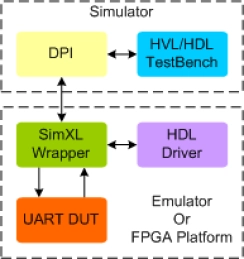

UART Synthesizable Transactor

- Fully compatible with 16550

- Supports transmit and receive commands allow the user to transmit and receive UART data

- Supports additional functionality of IRDA, RS232, RS422, RS485 and GPIO

- Supports full duplex operation

-

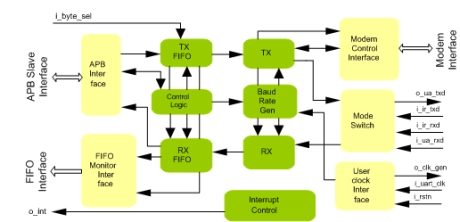

UART CONTROLLER IIP

- Implemented in Unencrypted Verilog, VHDL and SystemC

- Compliant with Standard UART 16550 Specification

- Full UART Functionality

- Transmit and receive commands allow the user to transmit and receive UART data

-

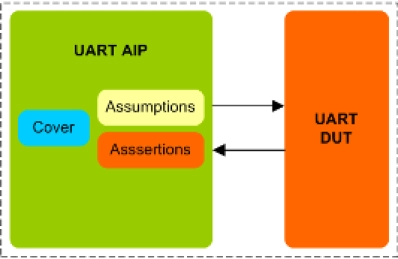

UART Assertion IP

- Specification Compliance

- Fully compatible with 16550.

- Transmit and receive commands allow the user to transmit and receive UART data.

- Support additional functionality of IRDA, RS232, RS422, RS485 and GPIO.

-

UART/IrDA controller with APB interface

- AMBA 2.0 APB bus support

- High-Speed NS 16C550A-Compatible UART

- IrDA 1.3 SIR with up to 115.2 Kbps data rate

- SIR pulse width is programmable as 1.6 us or a 3/16 of baud-rate pulse width

-

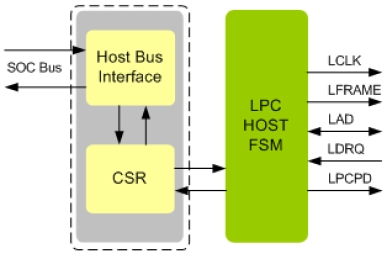

LPC Host IIP

- Compliant with version 1.1 LPC Specifications.

- Full LPC Host functionality.

- Supports the following operations:

- Memory read and write