IEEE 802.11 IP

Filter

Compare

37

IP

from

21

vendors

(1

-

10)

-

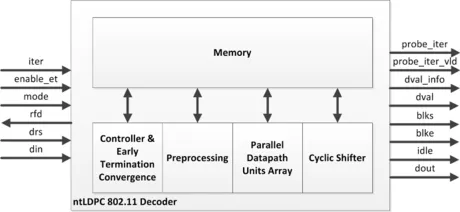

IEEE 802.11 n/ac/ax LDPC Decoder

- LDPC Decoder, support all IEEE 802.11 n/ac/ax defined block lengths (648, 1296, 1944) and code rates (1/2, 2/3, 3/4 and 5/6).

-

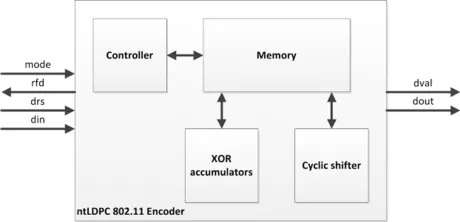

IEEE 802.11 n/ac/ax LDPC Encoder

- Encoder and decoder, support all IEEE 802.11 n/ac/ax de-fined block lengths (648, 1296, 1944) and code rates (1/2, 2/3, 3/4 and 5/6).

-

-

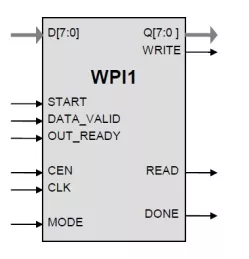

IEEE 802.11 WAPI Encryption Core

- Completely self-contained: does not require external memory

- Includes encryption, decryption, key expansion and data interface

- Support for WAPI WPI packet encapsulation

- Automatic generation of key context from key data

-

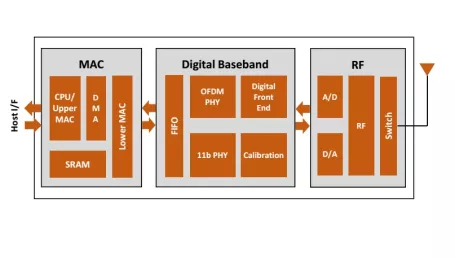

IEEE 802.11n RF/Baseband/MAC 40nm

- Supports WFA Wi-Fi Direct, Wi-Fi Aware PMF and WPS

- Frequency band: 2.4GHz

- Modulation modes: OFDM with BPSK, QPSK, 16-QAM,64-QAM, DSSS, CCK

- Supported data rates: IEEE 802.11b: 1 to 11Mbps, IEEE 802.11g: 6 to 54Mbps, IEEE 802.11n: 6.5 to 72.2Mbps

-

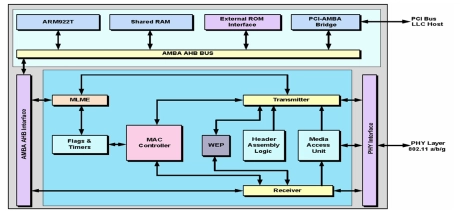

802.11 a b and g IEEE Standard - Wireless LAN

- The MAC core for Wireless LAN is compatible with 802.11 a b and g IEEE Standards.

- It is designed to handle packetized DSSS (Direct Sequence Spread Spectrum) and OFDM (Orthogonal Frequency Division Multiplexing) data transmissions; the software implementation supports all data rates.

- The MAC management or control functionality is implemented in firmware while the time critical functionality is implemented in hardware.

-

IEEE 802.11n/ac/ax Encoder and Decoder

- Fully synchronous design, using single clock

- Fully synthesizable drop-in module for FPGAs

- Optimized for high performance and low resources

- Low implementation loss

-

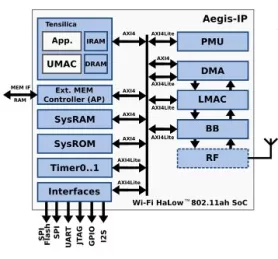

IEEE 802.11ah MAC/PHY

- 1 MHz and 2 MHz channel width

- S1G_1M, S1G_SHORT PPDU

- Mandatory MAC including TXOP, RID, SST, TWT, AID,…, RAW