IEEE 1588 IP

Filter

Compare

117

IP

from

28

vendors

(1

-

10)

-

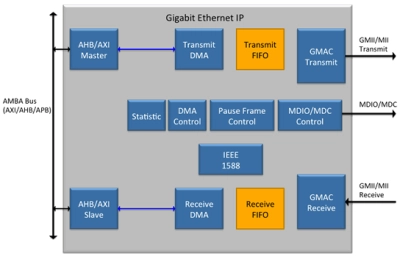

Gigabit Ethernet with IEEE 1588 and AVB

- The Gigabit Ethernet Media Access Controller IP is compliant with the Ethernet IEEE 802.3-2008 standard and supports protocol extensions for Audio Video Bridging (AVB).

- The Gigabit Ethernet IP provides a 10/100 Mbps Media Independent Interface (MII) and a 1000 Mbps Gigabit Media Independent Interface (GMII).

-

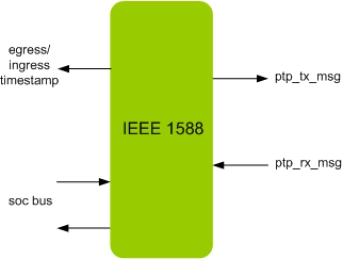

IEEE 1588 IIP

- Compliant with IEEE Standard 1588-2019 specification

- Supports for TSN required PTP as per IEEE 802.1AS

- Configurable as PTP Master or PTP Slave

- Supports both end to end and peer to peer delay mechanism

-

IEEE 1588 V2 CPU-less Slave Clock

- IP core netlist ready for seamless integration in ISE design flow

- Reference design for AVNET Spartan-6 FPGA LX9 Microboard

- Available profiles: Power, IEC 61850 and Telecom

-

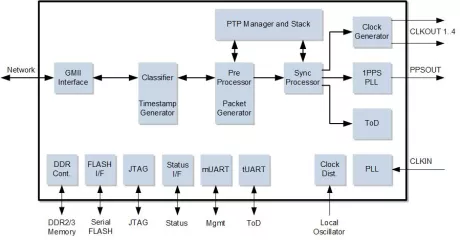

IEEE 1588 Boundary, Slave And Master Clock

- IEEE 1588 v2 compliant Boundary Clock and Master/Slave Ordinary Clock IP core

- ToD error is better than ±1µsec on a managed 10-switch GbE network under ITU-T G.8261 conditions

- Frequency accuracy performance is better than 16ppb on a managed 10-switch GbE network under ITU-T G.8261 conditions

- Standard compliant Best Master Clock (BMC) algorithm

-

IEEE 1588 Boundary, Slave And Master Clock

- Standalone IEEE1588v2 standard compliant BC and Master/Slave OC chip on FPGA

- Hybrid 1588/SyncE mode support

-

IEEE 1588 Boundary, Slave And Master Clock

- Standalone IEEE 1588 v2 standard compliant Boundary Clock (BC) and Ordinary Clock (OC) Master/Slave IP core for Xilinx Spartan-6

- Excellent synchronization performance over most extreme packet transport network conditions

- Slave meets 3G, 4G-LTE and 5G synchronization requirements

- Adaptive to network impairments

-

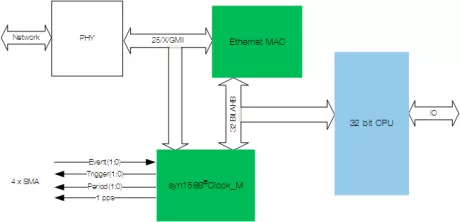

syn1588® enabled IEEE 1588 compliant clock synchronisation

- fully synchronous to the system clock

- all registers of the core operate with the rising clock edge

- well commented, structured VHDL source code

- medium footprint and medium I/O count

-

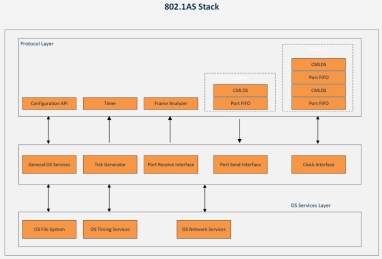

IEEE 802.1AS Software Stack

- The IEEE 802.1AS software stack implements the Timing and Synchronization protocol for time-sensitive applications over bridged and wireless networks.

- Based on a profile of the Precision Time Protocol (PTP) as defined in IEEE 1588, 802.1AS provides precise synchronization of clocks across all network devices, enabling accurate time distribution for Time-Sensitive Networking (TSN) and other real-time applications.

-

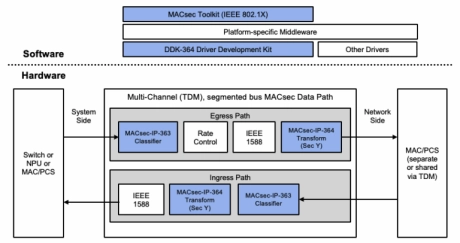

1.6T/3.2T Multi-Channel MACsec Engine with TDM Interface (MACsec-IP-364)

- The MACsec-IP-364 is a MACsec/IPsec engine developed specifically for high-speed, multi-rate and multi-port Ethernet devices.

- Its architecture provides an optimal multi-protocol solution for aggregate throughput for 1.6T and 3.2T.

- The MACsec-IP-364 is ideal for deployment in data center, enterprise and carrier network applications, as well as network-attached high-performance computing.