IEC 61508 IP

Filter

Compare

3

IP

from

2

vendors

(1

-

3)

-

First High-Performance GPU with Functional Safety

- Flexible Partitioning

- Virtualization

- Safety Enablement

-

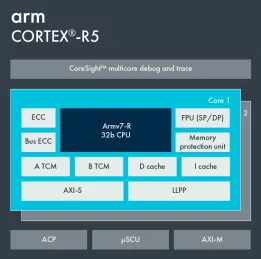

Arm Cortex-R5

- Higher system performance and Advanced system level integration features - Dual-core configurations which enable twice the performance with Accelerator Coherency Port (ACP) and Micro Snoop Control Unit (micro SCU) maintaining data cache coherency with DMA I/O for both cores.

- Improved reliability and safety features - Low-Latency Peripheral Port (LLPP), enhanced Memory Protection Unit (MPU) and enhanced ECC support.

- Lock-step configurations - Second core provides redundancy for safety critical applications.

- Extended functional safety support - Safety Documentation simplifies the certification effort for standards such as ISO26262 and IEC 61508, and enables higher levels of certifications.

-

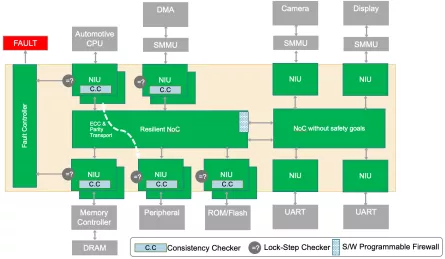

FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.

- ARM® Cortex®-R5 and Cortex-R7 processor port checking

- Hardware duplication and redundancy

- Custom ECC and parity generation and checking