I2S IP

Filter

Compare

133

IP

from

31

vendors

(1

-

10)

-

I2S to AHB bridge, following AMBA4 specifications

- dos_I2S_AHB_bridge is an I2S to AHB bridge, following AMBA4 specifications

-

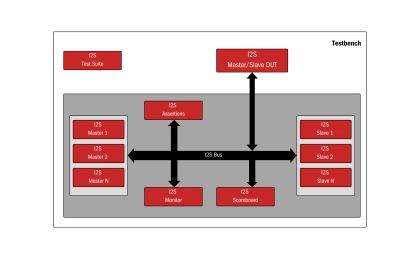

I2S - Ensures proper audio data transmission, synchronization, and integrity

- I2S (Inter-IC Sound) is a serial bus interface used for connecting digital audio devices. As a Verification IP (VIP), it ensures proper data transmission, signal integrity, timing, and protocol compliance in audio communication systems.

- This VIP verifies key elements such as word length, frame synchronization, clock behavior, and error handling, making it essential for testing I2S communication in a range of applications, including consumer electronics, automotive, and medical devices

-

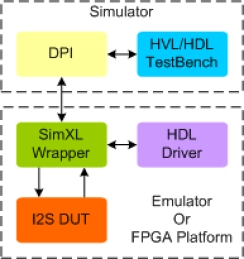

Simulation VIP for I2S

- Configurability

- Fully configurable VIP configuration: Manager/Subordinate, Transmitter/Receiver, Active/Passive

- Word Length Programmability

- Supports 8, 12, 16, 20, 24, 32, and user-defined

-

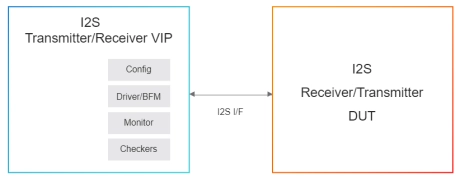

I2S Verification IP

- Complies with Philips I2S Specification June 5, 1996

- Full I2S Transmitter, Receiver and Controller functionality

- Supports up to 32 channels in transmit path

- Supports up to 32 channels in receive path

-

I2S Synthesizable Transactor

- Supports Philips I2S Bus Specification June 5, 1996

- Full I2S Transmitter, Receiver and Controller functionality

- Supports up to 32 channels in transmit path

- Supports up to 32 channels in receive path

-

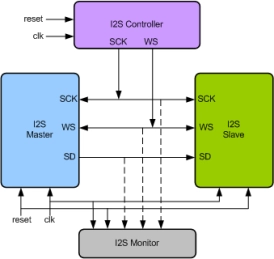

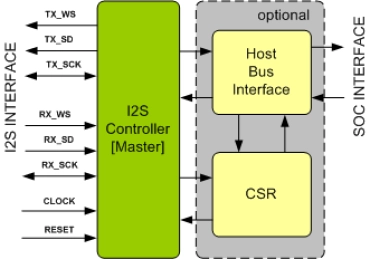

I2S Controller IIP

- Compliant with the Philips I2S Bus Specification

- Master mode as Controller

- Slave mode as transmitter and receiver

- Bidirectional operation through two unidirectional serial data lines

-

I2S PHY & Controller

- DTI I2S Controller provides an interface between system bus and Inter-IC Sound devices.

- The controller is compliant with NXP Inter-IC Sound Bus Specification and AMBA APB Specification.

- Other bus protocols such as AXI-Lite, AHB-Lite, etc are optionally supported.

-

Audio I2S

- AXI4S Compliant

- Can be configured up to 4 I2S interfaces, each channel supporting 2 audio channels

- Can be configured up to 4 stereo or 8 independent channels

- 16/24 bit data support

-

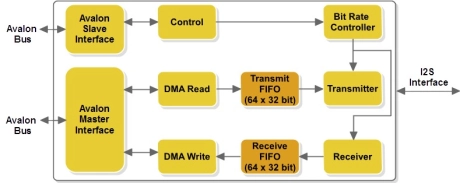

I2S Receiver/Transmitter

- Configurable structure

- OPB V2.0 bus interface for access into internal registers

- PLB V3.4 bus interface for off-chip memory access

- Adjustable memory interface width 16, 32, or 64 bits

-

I2S Controller

- I²S Controller is designed to transfer audio data to and from Audio codec.

- It can be configured as both Master and Slave mode using software.

- The I²S IP is Phillips Inter IC Sound (I²S) specification compliant core for Altera devices.