I2C/SPI Controller IP

Filter

Compare

42

IP

from

16

vendors

(1

-

10)

-

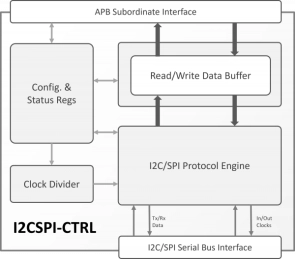

I2C and SPI Master/Slave Controller

- The I2CSPI-CTRL is a compact and versatile serial interface controller supporting both SPI (Serial Peripheral Interface) and I2C (Inter-Integrated Circuit) protocols.

- Its low silicon resource requirement makes it suitable for area-constrained and low-power applications, while its software compatibility with Microchip’s MSSP peripheral eases use and software integration.

-

DMA Controller

- DTI_DMA control the DMA transfers data between different points in the memory space without intervention of the CPU.

- The DMA is generally used to replace two CPU functions: memory copy and transfer data between memory and peripheral (peripheral devices such as SPI, UART, GPIO, I2C, I2S, WDT, etc.)

-

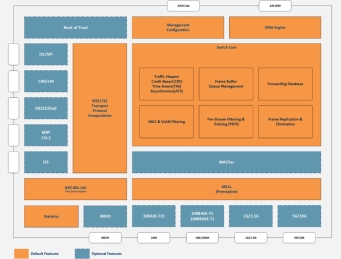

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

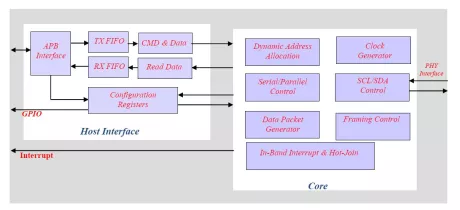

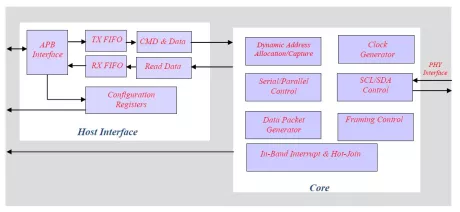

MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification

- Conforms to MIPI I3C v1.1 specifications

- MIPI Manufacturer ID: 0x03B3

- Dynamic Addressing while supporting Static Addressing for Legacy I2C Devices

- Legacy I2C messaging

-

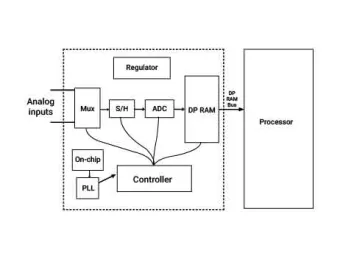

Analog Data Acquisition Controller IP

- AXI4-Lite standard user interface. Connects as a 32-bit slave on AXI interface

- User configurable acquisition parameters: Sampling frequency, number of samples in bursts.

- Programmable ADC interface to connect different types of ADCs in addition to analog multiplexers to connect multiple analog channels

- Optimized power consumption

-

MIPI I3C Master Controller

- Compliant with the latest MIPI I3C specification

- Backward compatible with the I2C slave devices

-

MIPI I3C Slave Controller

- Compliant with the latest MIPI I3C specification

- Backward compatible with the I2C slave devices

- Supports all data rates up to 26.7 Mbps

- Optional High Data Rate messaging Modes (HDR)

-

16Bit 91dB Audio CODEC with headphone drivers and PWM Controller, SMIC0.18um

- DAC 91dB SNR, ADC 85dB SNR Audio Mono CODEC

- PWM Controller for Class-D Amplifier Configuration

- Capacitor-less dual channel headphone Output

- 8KHz to 48KHz Sampling Frequency

-

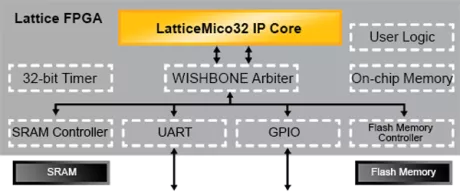

Generic Platform IP for Micro-Controllers

- Supports AndesCore™ N7/N8/N9/N10

- Provides two bus structures

- Provides interfaces for design extension/integration

-