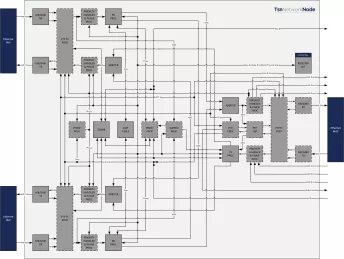

HSR PRP Switch IP

Filter

Compare

8

IP

from

3

vendors

(1

-

8)

-

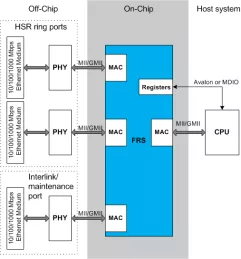

Network Redundancy (HSR & PRP) core

- Supports the HSR and PRP redundancy protocol according to IEC62439-3 rev 3

-

Managed Redundant Switch

- Full-Duplex Ethernet 10/100/1000.

- Half-Duplex Ethernet 10/100.

- Configurable 3 to 16 Ethernet ports.

- MII/GMII/RGMII interfaces for attaching to an external Physical Layer device (PHY).

-

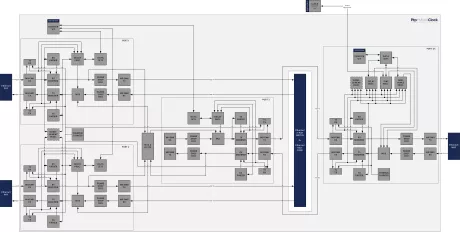

HSR-PRP Switch

- Fast Ethernet (100Mb) and Gigabit (1GB) versions available

- It switches frames by hardware. This feature offers high switching speeds, needed to fulfill the Maximum Allowed Age and Data Integrity set for Process Bus and Inter-bay Bus in Electric Substation Automation

- The processing architecture has been designed specifically for HSR/PRP. Forwarding latencies in range of 500ns for Gigabit Ethernet

- It is an all-hardware. There is no need for on-chip microprocessor nor software stack

-

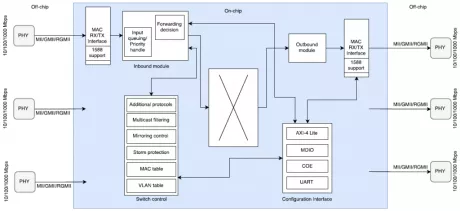

Managed Ethernet Switch

- Full-Duplex Ethernet 10/100/1000.

- Half-Duplex Ethernet 10/100.

- Configurable 3 to 16 Ethernet ports.

- MII/GMII/RGMII interfaces for attaching to an external Physical Layer device (PHY).

-

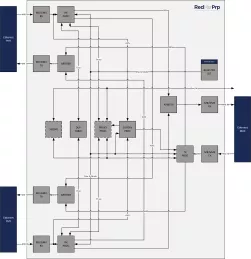

Triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocols, providing seamless redundancy for Ethernet networking

- Triple-speed (10Mbps/100Mbps/1Gbps), full-duplex operation on all ports

- Compatible with IEC 62439-3 Clause 5 “High-availability Seamless Redundancy (HSR)”

- Compatible with IEC 62439-3 Clause 4 ”Parallel Redundancy Protocol (PRP)”

- Time and frequency synchronization using IEEE1588-2008 Precision Time Protocol v2

-

Time Sensitive Networking (TSN) Switched End Node core

- Up to 8 different priority queues, with freely definable VLAN priorities

- Up to 8 phases per cycle according to priority queues

-

Time Synchronization Redundancy

- PTP: Ethernet. PTP Slave at the input.

- IRIG-B: IRIG-B compliant signal. IRIG-B Slave at the input.

-

IEEE1588 & IEEE802.1AS PTP Hybrid Clock (HC) core

- Combined PTP Ordinary Clock and PTP Transparent Clock according to IEEE1588-2008

- Intercepts path between MAC and PHY

- Two (TC) plus one (OC) Port, used for daisy chaining or redundancy protocols

- Synchronization accuracy: +/- 25ns