HBM2 PHY IP

Filter

Compare

14

IP

from

4

vendors

(1

-

10)

-

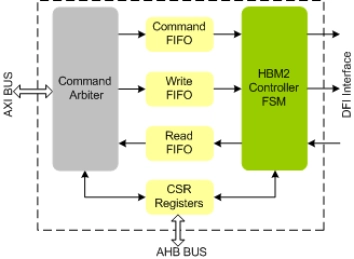

HBM2 Controller IIP

- Supports HBM2 protocol standard JESD235 and JESD235A Specification

- Compliant with DFI version 4.0 or 5.0 Specification.

- Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

HBM2E PHY V2 - TSMC N5

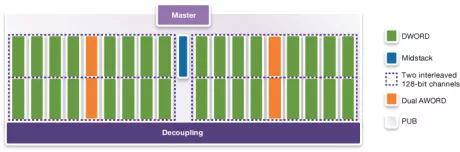

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 - TSMC 7FF18

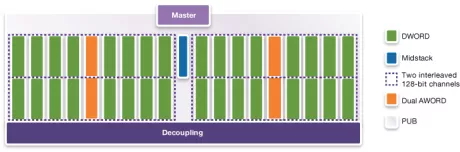

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 - TSMC 6FF18

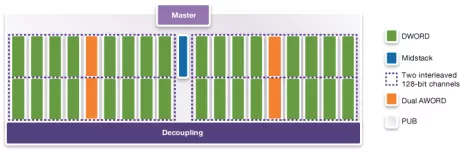

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 (Hard 1) - TSMC 7FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 (Hard 1) - TSMC 6FF18

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 (Hard 1) - TSMC 5FF12

- Complete HBM2/HBM2E IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market

- 2.5D interposer expertise and reference designs

- Supports 2.5D-based JEDEC standard HBM2/HBM2E SDRAMs with data rates up to 3200 Mbps

-

HBM2E PHY V2 in TSMC (N7, N6, N5)

- Low latency, small area, low power

- Compatible with JEDEC standard HBM2/HBM2E SDRAMs

- Data rates up to 2400 Mbps for HBM2 and 3600 Mbps for HBM2E

- 4H and 8H HBM2/HBM2E SDRAM stacks supported

-

HBM2E PHY V2 (Hard 1) in TSMC (N7, N6, N5)

- Low latency, small area, low power

- Compatible with JEDEC standard HBM2/HBM2E SDRAMs

- Data rates up to 2400 Mbps for HBM2 and 3600 Mbps for HBM2E

- 4H and 8H HBM2/HBM2E SDRAM stacks supported

-

TSMC CLN7FF HBM2E PHY IP

- High Bandwidth Memory (HBM2E) DRAM PHY

- Supports HBM 3.2Gbps

- Supports DFI 1:2

- Supports only BL4