HBM controller IP

Filter

Compare

83

IP

from

13

vendors

(1

-

10)

-

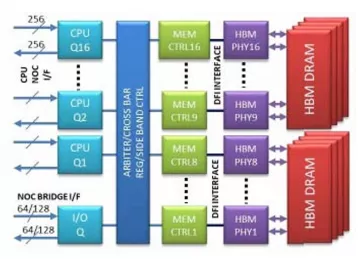

HBM Memory Controller

- Low latency, high bandwidth

- Supports HBM or DDRx memory types

- 16 parallel access channels

- Multi, independent internal queues

-

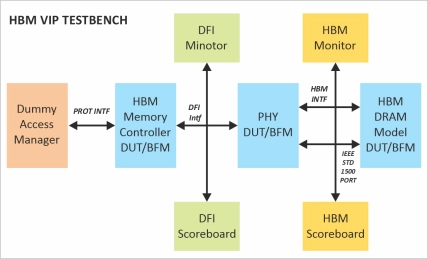

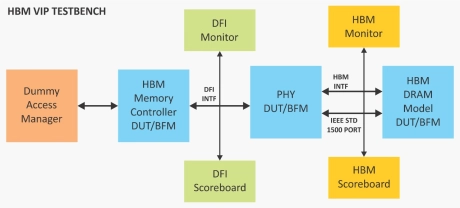

HBM 4 Verification IP

- The HBM4 Verification IP provides an effective & efficient way to verify the components interfacing with HBM interface of an ASIC/FPGA or SoC.

- The HBM4 VIP is fully compliant with Standard HBM Version JESD270-4 specifications from JEDEC.

- This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design time and the simulation time.

-

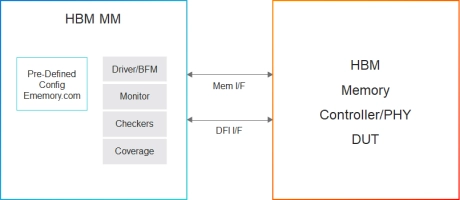

Verification IP for HBM

- HBM VIP is a comprehensive memory VIP solution portfolio for high bandwidth memory (HBM), targeting a new standard in memory performance, density, power consumption, and cost.

- HBM VIP is intended for SoC and memory control ler designers who employ external HBM modules and PHY developers to ensure both comprehensive verification and protocol and timing compliance.

-

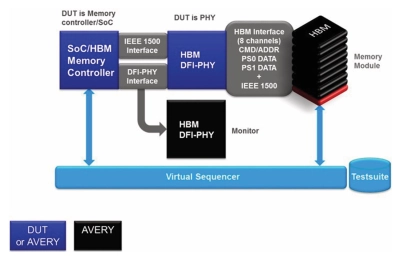

Simulation VIP for HBM

- Speed (MHz)

- 1800MHz (3.6 Gbps/pin)

- Device Density

- Supports a wide range of device densities from 1Gb to 24Gb

-

HBM 3 Verification IP

- Compliant to JEDEC HBM SDRAM Specification versionJESD235A.

- Supports Legacy and Pseudo Channel Mode.

- Supports connection to any HBM Memory Controller IPcommunicating with a JESD235A compliant HBM Memory Model.

- Available in all Stack memory size from 8 Gb to 32 Gb (8Channels/Stack).

-

HBM3 V2 Solution enabling access to HBM3 Controller and HBM3 PHY in TSMC N3E

- JEDEC HBM 3.0 DRAM

- DFI 5.0 compliant interface to HBM3 PHY

- Multiport Arm® AMBA® interface (4 AXI AXI™) with managed QoS or single-port host interface, per pseudo-channel

- Data rates up to 6.4 Gbps (DFI 1:1:2) (1.6GHz controller clock)

-

HBM3 Solution enabling access to HBM3 Controller in TSMC N5 1.2V

- JEDEC HBM 3.0 DRAM

- DFI 5.0 compliant interface to HBM3 PHY

- Multiport Arm® AMBA® interface (4 AXI AXI™) with managed QoS or single-port host interface, per pseudo-channel

- Data rates up to 6.4 Gbps (DFI 1:1:2) (1.6GHz controller clock)

-

HBM3 Solution enabling access to HBM3 Controller and HBM3 PHY in TSMC N5 1.2V

- JEDEC HBM 3.0 DRAM

- DFI 5.0 compliant interface to HBM3 PHY

- Multiport Arm® AMBA® interface (4 AXI AXI™) with managed QoS or single-port host interface, per pseudo-channel

- Data rates up to 6.4 Gbps (DFI 1:1:2) (1.6GHz controller clock)

-

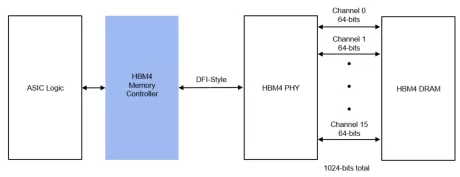

HBM4 Memory Controller

- Supports HBM4 memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 10 Gbps/pin

- Refresh Management (RFM) support

- Maximize memory bandwidth and minimizes latency via Look Ahead command processing

- Integrated Reorder functionality

-

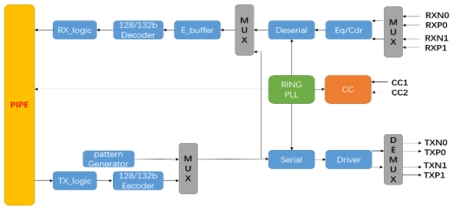

USB3.2 PHY & Controller

- USB is the ubiquitous interconnect standard of choice for a wide range of computing and consumer applications

- Innosilicon provides a comprehensive set of software drivers to support commonly used USB peripherals

- In addition, our established USB ecosystem—comprising USB silicon suppliers, design IP houses, and verification and testing vendors—helps reduce development and production costs for USB host and peripheral manufacturers