Ethernet PHY IP

Filter

Compare

523

IP

from

63

vendors

(1

-

10)

-

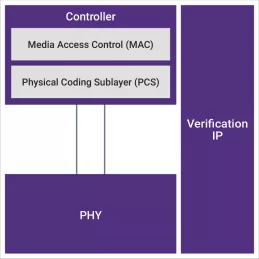

Ethernet PHY IP

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

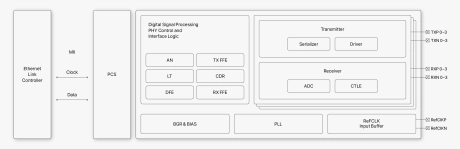

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

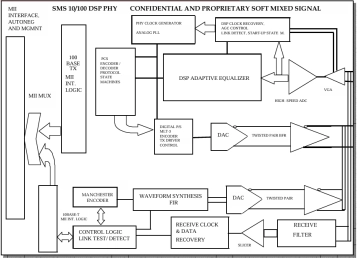

- DSP-based architecture using high-performance ADC/DAC for RX/TX

-

-

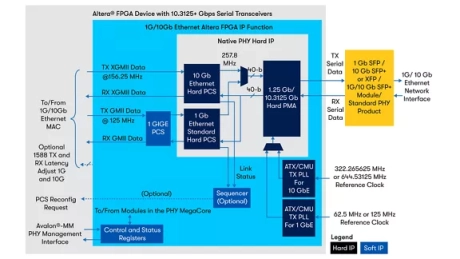

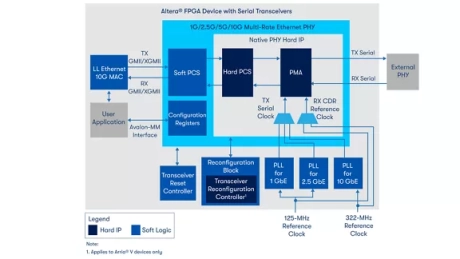

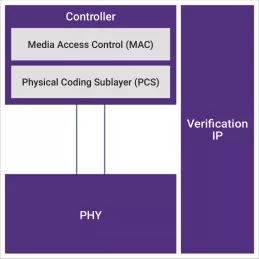

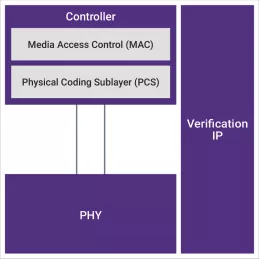

1G/10Gb Ethernet PHY Intel® FPGA IP

- The 1G/10G Ethernet PHY Intel® FPGA Intellectual Property (IP) core supports functionality of both the standard physical coding sublayer (PCS) and the higher data rate 10G PCS with an appropriate physical medium attachment (PMA)

- The Standard PCS implements the 1GbE protocol as defined in Clause 36 of the IEEE 802.3 2005 Standard and also supports auto-negotiation as defined in Clause 37 of the IEEE 802.3 2005 Standard

- The 10G PCS implements the 10G Ethernet protocol as defined in the IEEE 802.3 2005 standard.

-

Multi-Rate Ethernet PHY FPGA IP

- The Multi-Rate Ethernet PHY FPGA IP core can dynamically support multiple data rates without any design regeneration or device reconfiguration

- This IP allows the creation of a 1G to 10G configuration that allows dynamic reconfiguration across all Ethernet rates from 10M, 100M, 1G, 2.5G, 5G, and 10G.

-

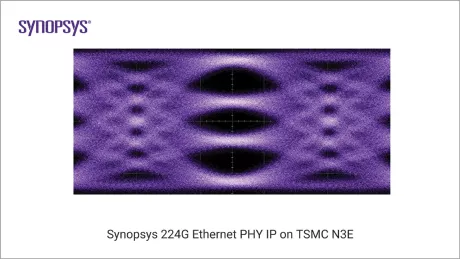

224G Ethernet PHY, TSMC N3P x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

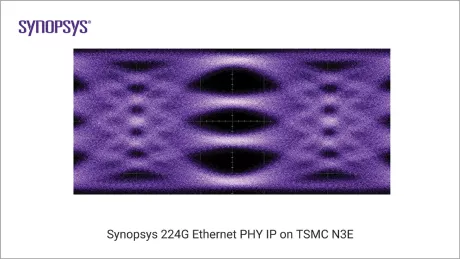

224G Ethernet PHY, TSMC N2P x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

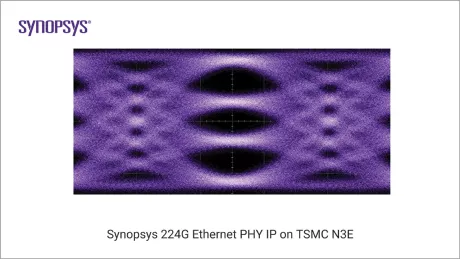

224G Ethernet PHY, Intel 18A x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 224Gbps data rates

- Enables 200G, 400G, 800G, and 1.6T Ethernet

- Ethernet interconnects for wired network infrastructure

- Supports IEEE 802.3 and OIF-224G standards electrical specifications

-

112G Ethernet PHY, TSMC N7 x4, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x2, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects

-

112G Ethernet PHY, TSMC N7 x1, North/South (vertical) poly orientation

- Supports full-duplex 1.25 to 112Gbps data rates in several lane configurations

- Enables 100G, 200G, 400G, 800G Ethernet interconnects for wired and optical network infrastructure

- Supports IEEE 802.3ck and OIF standards electrical specifications

- Meets the performance requirements of multi-die, co-packaged optics, near-packaged optics, chip-to-chip, chip-to-module, and backplane interconnects