Embedded Vision Processor IP

Filter

Compare

15

IP

from

10

vendors

(1

-

10)

-

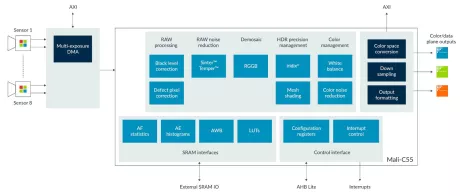

Image signal processor to advance vision systems for IoT and embedded markets

- Multi-sensor interface with up to 20-bit linear video input

- Up to 8 independent camera sources of max resolution 48 Megapixels / 8K (8192 x 6144)

-

ARC EV Processors are fully programmable and configurable IP cores that are optimized for embedded vision applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

Tensilica Vision P6 DSP

- 1024/512b Load/Store capabilities

- 256 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing

-

Tensilica Vision Q8 DSP

- 2048/1024b Load/Store capabilities

- 1024 8-bit MAC: 2X MAC capability versus Vision Q7 DSP

- 8/16/32-bit fixed-point processing

- Double-precision (FP64), single-precision (FP32), and half-precision (FP16) floating-point processing

-

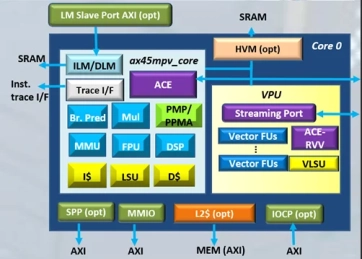

64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- 64-bit in-order dual-issue 8-stage CPU core with up to 1024-bit Vector Processing Unit (VPU)

- Symmetric multiprocessing up to 8 cores

-

Machine Learning Processor

- Extending Performance and Efficiency

- Flexible Integration

- Unified Software and Tools

-

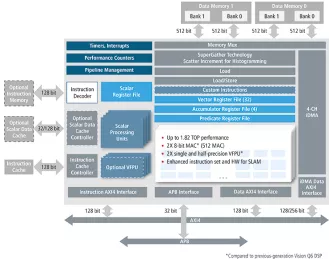

Tensilica Vision Q7 DSP

- Doubles Vision and AI Performance for Automotive, AR/VR, Mobile and Surveillance Markets

-

Deep Learning Processor

- High performance: Whether it’s at the edge or in the cloud, videantis' processors provide the required performance.

- Scalable architecture: 1 to 1000+ cores address ultra-low cost to high-performance applications.

- Ultra-high MAC throughput: Each core computes a high number of MACs per cycle, resulting in an abundant amount of processing performance in multi-core systems.

-

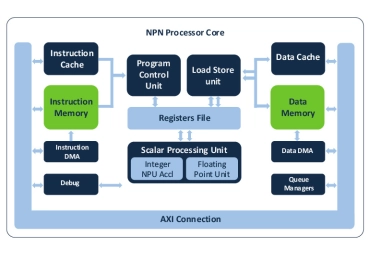

NPU IP for Embedded ML

- Fully programmable to efficiently execute Neural Networks, feature extraction, signal processing, audio and control code

- Scalable performance by design to meet wide range of use cases with MAC configurations with up to 64 int8 (native 128 of 4x8) MACs per cycle

- Future proof architecture that supports the most advanced ML data types and operators

-

Hyper-Bandwidth Multichannel Memory Subsystem

- Hyper-Bandwidth Multi-Channel - The fastest, most observable LPDDR3 subsystem you can drop into an SoC

- Supports an aggressive bandwidth envelope for LPDDR3, JEDEC-2133Mbps and up to 3200 Mbps on select process nodes.

- Includes hard QoS enforcement, traffic shaping, performance observability & self-tuning PHY front-end.