ECC Accelerator IP

Filter

Compare

57

IP

from

16

vendors

(1

-

10)

-

ECC Secure Accelerator - High-performance ECC IP with advanced physical security

High-performance ECC IP with advanced physical security

-

ECC Secure Accelerator - Compact and Secure ECC IP Core for Resource-Constrained Devices

- Compact and Secure ECC IP Core for Resource-Constrained Devices

-

Crypto Box Toolset Secure Accelerator

- The High-Performance Hybrid Crypto Box IP core delivers maximum cryptographic throughput by combining classical asymmetric (RSA, ECC), symmetric (AES), and hashing (SHA-2/HMAC) engines with a dedicated post-quantum accelerator supporting ML-KEM (Kyber) and ML-DSA (Dilithium).

- Designed for performance-critical systems without tight area or power limitations, this IP enables ultra-fast key exchange, digital signatures, and secure data processing.

-

Crypto Box Toolset Secure Accelerator

- The Hybrid Crypto Box IP core is a comprehensive, high-efficiency cryptographic solution that combines RSA, ECC, AES, and SHA-2/HMAC with a built-in accelerator for post-quantum algorithms such as ML-KEM (Kyber) and ML-DSA (Dilithium). Designed for embedded systems with balanced resource constraints, it enables secure key exchange, digital signatures, authenticated encryption, and hashing, future-proofed for the quantum era.

-

Crypto Box Toolset Secure Accelerator

- The Crypto Box IP core is a high-efficiency cryptographic solution that combines RSA, ECC, AES, and a SHA-2/HMAC engine, all with advanced protections against side-channel and fault injection attacks.

- Designed for devices with balanced budgets for performance, area, and power, it enables secure key exchange, digital signatures, data encryption, and message authentication in a unified, compact architecture.

-

Crypto Box Toolset Secure Accelerator

- The Crypto Box IP core is a compact, power-efficient cryptographic engine that combines essential asymmetric algorithms (RSA, ECC) with high-speed AES encryption in a single integrated block.

- Designed for resource-constrained embedded systems, it enables secure key exchange, digital signatures, and fast data encryption with minimal area and power overhead.The

-

Asymmetric cryptographic accelerator

- The ACrypto Engine is an asymmetric cryptographic accelerator suitable for embedded application.

- It provides capability for basic arithmetic and frequently used operations. Along with driver, it is flexible to support popular upperlayer applications.

-

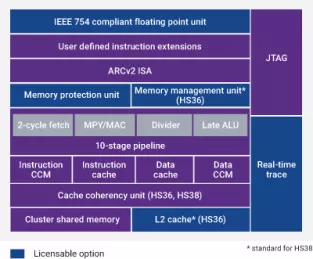

The FastMath Pack is a math processing accelerator for the ARC HS family

- Achieves up to 3232 DMIPS and 6681 CoreMarks* at 1.61 GHz on 28HPM (single-core configuration, worst case silicon and conditions)

- Delivers 2.13 DMIPS/MHz, 4.15 CoreMarks/MHz* (per core)

- High-speed, 10-stage pipeline

- Up to 16MB instruction and data close coupled memory (CCM)

-

Agile PQC Public Key Accelerator

- Agile IP comprised of HW/FW/SW, adaptable to future standards’ evolution

- Highly configurable IP can be tuned for specific applications with most optimal PPA

- Scalable PQC PKA IP complies with latest NIST PQC algorithms

-

Agile Post Quantum Crypto (PQC) Public Key Accelerator - NIST algorithms

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)