Display Processing IP

Filter

Compare

103

IP

from

24

vendors

(1

-

10)

-

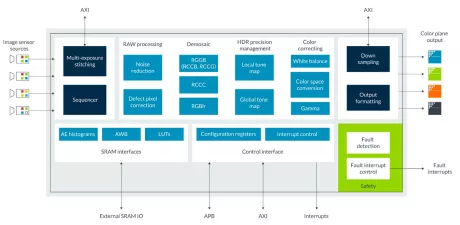

Image Signal Processing for ADAS and Display Applications

- Multi-Camera Support

- Advanced Image Processing

- Every Pixel Reliable

-

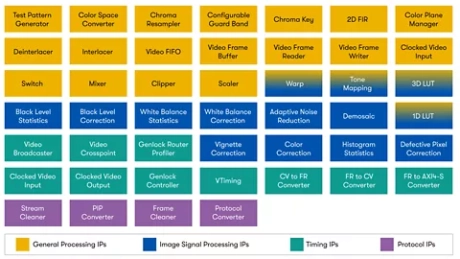

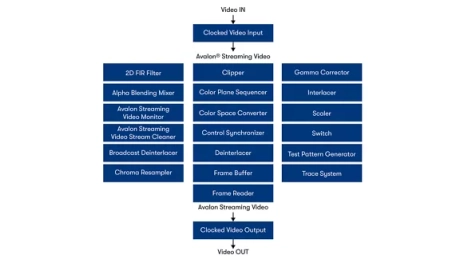

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

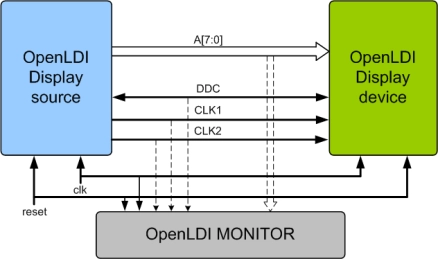

Open LVDS Display Interface (OpenLDI) Verification IP

- Full OpenLDI Display Source and Display Device functionality.

- Supports OpenLDI v0.95 specification

- Supports 8 serial data lines (A0 through A7) and two clock lines (CLK1 and CLK2) in the OpenLDI interface.

- Supports DDC2B protocol to retrieve the EDID data structure from display.

-

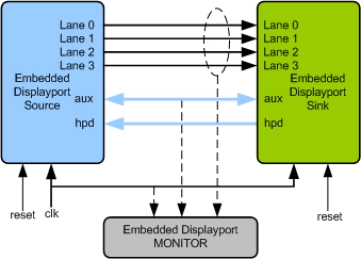

Embedded Display Port Verification IP

- Full Embedded Display port source device and sink device functionality.

- Embedded Display port v1.3,1.4,1.4b and 1.5 compliant and based on display port specs 1.2/1.2a/1.3/1.4/2.0.

- Support transmitter and receiver Mode.

- Supports multi lanes upto 4 lanes.

-

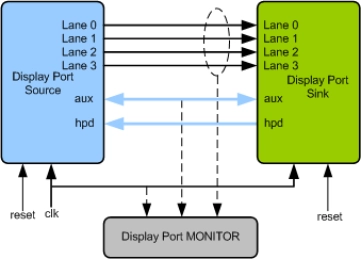

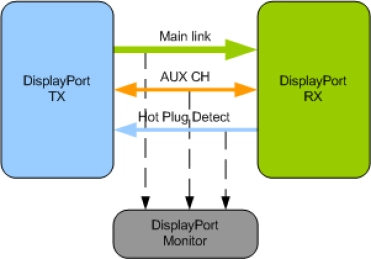

Display Port 2.0 Verification IP

- Full Display port 2.0 source device and sink device functionality.

- Supports backward compatibility with previous versions upto DPv1.4a

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing.

-

Display Port Verification IP

- Full Display port source device and sink device functionality.

- Display port supports version 1.0,1.1,1.2,1.2a,1.3,1.4,1.4a and 2.0 specification.

- Supports multi lanes upto 4 lanes.

- Supports control symbols for framing(Both Default & Enhanced framing mode).

-

High-quality and powerful display processor

- Support 8K@60FPS or multiple 4K@120FPS

- All common HDR formats, including HDR10, HDR10+ and HLG

- Security Features for Content Protections

- Subjective and objective image quality

-

Video Post Processing IP (cropping, color space conversion (CSC), alpha blending, 3D LUT, and flexible resizing)

- The PC820 pixel processor is an IP which provides pixel processing functions such as cropping, color space conversion (CSC), alpha blending, 3D LUT, and flexible resizing.

- It supports input data of various compressed or uncompressed RGB and YUV formats.

- After being processed by the pixel processor, the data can be output in uncompressed, compressed, or normalized formats.

-

2D GPU IP Core - Target Display Resolution: 8K

- Xwindow (EXA)

- Hardware Composer (HWC)

- DirectFB

- Pixel Rate (Pixels/Cycle): 4

- Target Display Resolution: 8K

- Direct 3D Tile Status and Buffer Option: yes

- Formats Support: RGB & YUV FP16/32