Datapath IP

Filter

Compare

247

IP

from

39

vendors

(1

-

10)

-

SATA Bridge Platform (Optional: AES, Hardware Datapath)

- Fully compliant to SATA 1.5Gb/s, 3Gb/s, and 6Gb/s specifications (SATA 3.3).

- Independent host and device SATA speed negotiation.

- Software extensible bridging platformCommand set support for Windows, along with standard Linux discovery and communication.

- Boot Device Capable.

-

UDP Offload Engine for IPv6

- Full IPv6 support including Echo, NDP, MLD

- Line-rate UDP/IPv6 transmit and receive

- RFC 768 & RFC 8200 compliant

- Packet parsing and header synthesis in hardware

-

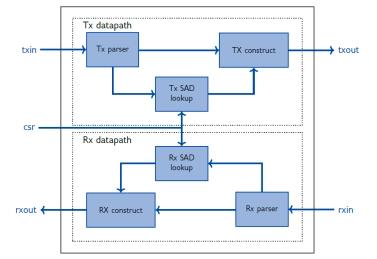

IPSEC AES-256-GCM (Standalone IPsec)

- XIP7213E implements the Internet Protocol Security (IPsec) as standardised in RFC4303 and RFC4305.

- The IPsec protocol defines a security infrastrucure for Layer 3 (as per the OSI model) traffic by assuring that a received packet has been sent by the transmitting station that claimed to send it.

-

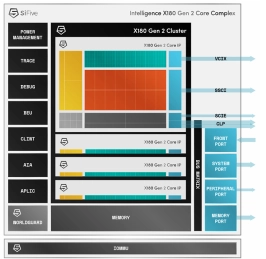

Multi-core capable 64-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.

-

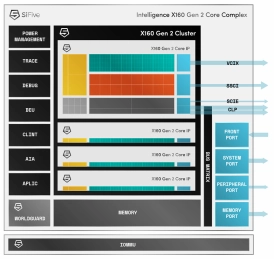

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

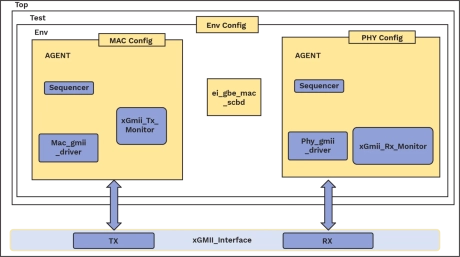

100G Ethernet Verification IP

- The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems.

- Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards.

- Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.

-

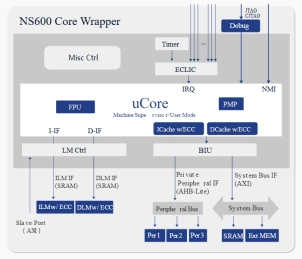

32-Bit Security processor

- Nuclei Security processor is a series of chips designed specifically for security application scenarios, including NS100, NS300, and NS600 products.

-

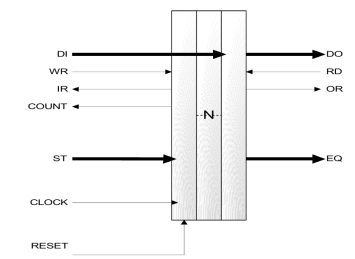

Searchable Synchronous FIFO

- The FIFO-CAM controls are designed to operate over a wide range of clock frequencies.

- The interface signals are fully synchronous; no asynchronous signals are present on either side.

- Only reset may be asynchronous in that it may be asserted asynchronously and synchronized internally to the clock.

-

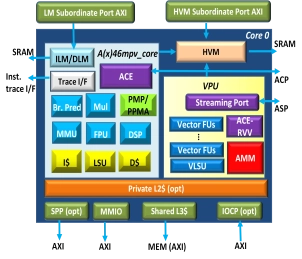

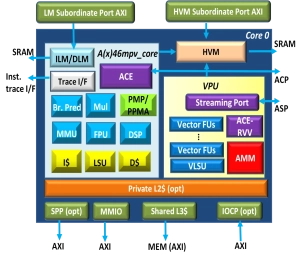

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.