Data Flow Processor IP

Filter

Compare

68

IP

from

33

vendors

(1

-

10)

-

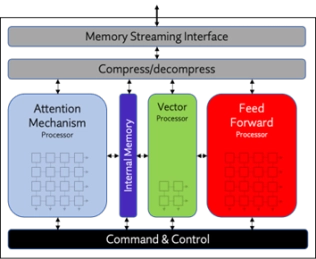

NPU IP Core for Data Center

- Origin Evolution™ for Data Center offers out-of-the-box compatibility with popular LLM and CNN networks. Attention-based processing optimization and advanced memory management ensure optimal AI performance across a variety of today’s standard and emerging neural networks. Featuring a hardware and software co-designed architecture, Origin Evolution for Data Center scales to 128 TFLOPS in a single core, with multi-core performance to PetaFLOPs.

-

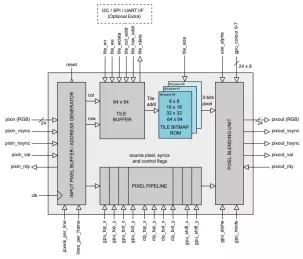

Graphics Processor Overlay IP Core

- Technology independent soft IP Core for FPGA, ASIC and SoC devices

- Supplied as human-readable VHDL (or Verilog) source code

-

-

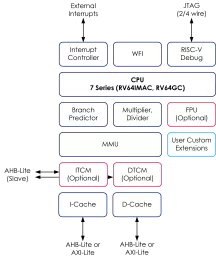

Baseband processor

- The Ceva-BX2 baseband processor IP handles both signal-processing and control workloads with up to 16 GMACs per second performance and high-level-language programming.

- It supports a range of integer and floating-point data types for a wide range of baseband applications like 5G PHY control, and exploits a high degree of parallelism, but with remarkably compact code size.

- Optimized high-speed interfaces expedite connection to other Ceva cores or to accelerators.

-

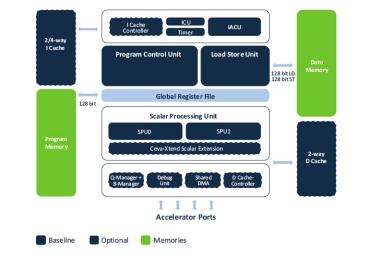

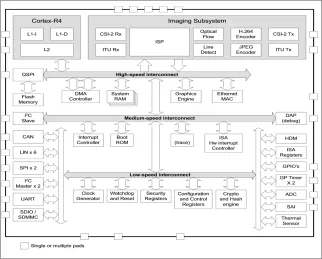

Image Signal Processor (5MP, 2X Sensors) IP

- Self-contained, no external memory needed

- ARM® Cortex-R4 CPU @500 MHz

- Up to 2 Mbytes of SRAM

- Up to 4 Mbytes of stacked Flash or 16 Mbyte external Flash with update via communication interfaces

-

Scalable and flexible display processor

- Leading Performance per Area

- Extreme Low Power Design

- Display Output

- AXI bus Interfaces

-

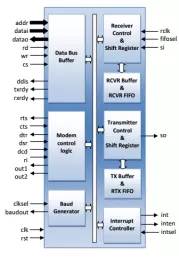

Configurable UART with FIFO, software and hardware flow control

- Software compatible with 16450, 16550,16650,16750 and 16950 UARTs

- Configuration capability

- Separate configurable BAUD clock line

- Majority Voting Logic

-

Configurable UART with FIFO, hardware and software flow control

- Software compatible with 16752 UARTs

- Configuration capability

- Dual channel UART - configurable

- Separate configurable BAUD clock line

-

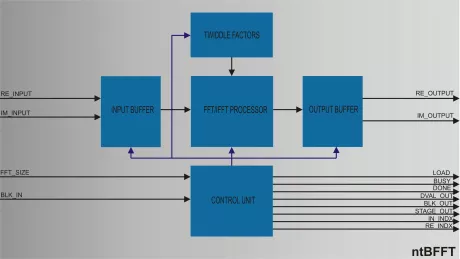

Fully Configurable Radix 2 FFT/IFFT Processor

- Radix-2 Fast Fourier Transform processor IP Core.

- Same IP core may be used to compute both FFT and IFFT transforms without any complexity overhead.

- Highly parameterizable/scalable design using generic I/O fixed point precision and generic internal calculations precision.

- Bit true Matlab script model is provided to aid core fixed point precision configuration for any target application.

-

Expanded UART with FIFO, hard and soft flow control, synchronous mode

- Software compatible with 16450, 16550,16650,16750 and 16950 UARTs

- Configuration capability

- Separate configurable BAUD clock line

- Majority Voting Logic