DSP IP

Filter

Compare

374

IP

from

69

vendors

(1

-

10)

-

HiFi iQ DSP

- 8X Increased AI Performance: Run the entire voice AI networks efficiently with configurable AI-MAC

- 2X Increased Raw Compute Performance: Wider SIMD allows more computations

- Expanded Data Type Support: Efficiently run cutting-edge voice AI models in FP8, BF16, and more

-

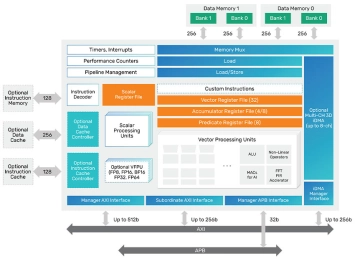

Tensilica ConnX 120 DSP

- Certified ISO 26262:2018 ASIL-compliant

- VLIW parallelism issuing multiple concurrent operations per cycle

- 256-bit SIMD

- Up to 64 MAC

-

-

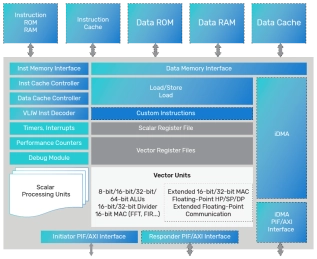

5G IoT DSP

- The XC21 is the most efficient vector DSP core available today for communications applications.

- The XC21 DSP is designed for low-power, cost- and size-optimized cellular IoT modems, NTN VSAT terminals, eMBB and uRLLC applications.

- Ceva-XC21 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, yet more cost and power efficient cellular devices

-

5G RAN DSP

- The XC23 is the most powerful DSP core available today for communications applications. The-XC23 offers scalable architecture and dual thread design with support for AI, addressing growing demand for smarter, more efficient wireless infrastructure

- Targeted for 5G and 5G-Advanced workloads, the XC23 has two independent execution threads and a dynamic scheduled vector-processor, providing not only unprecedented processing power but unprecedented utilization on real-world 5G multitasking workloads.

-

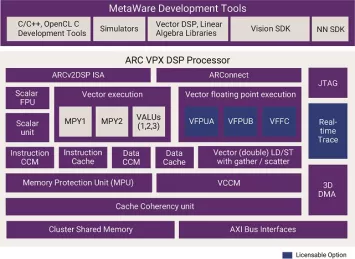

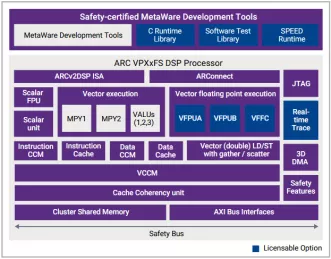

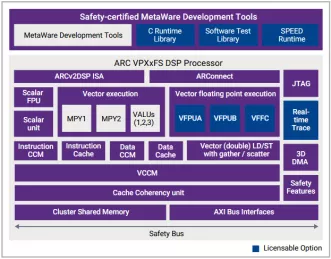

512-bit Vector DSP IP, Single Core with Functional Safety

- Integrated hardware safety features with minimal area and power impact for full ASIL compliance (ASIL D systematic, up to ASIL C random)

- Four-way VLIW architecture combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector lengths

- 8, 16, and 32-bit integer SIMD engines

-

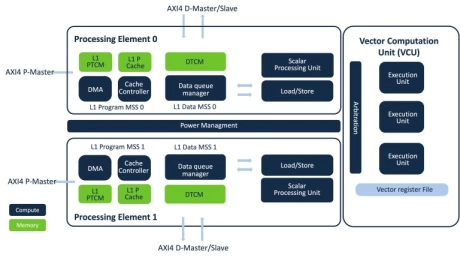

512-bit Vector DSP IP, Quad Core with Functional Safety

- Integrated hardware safety features with minimal area and power impact for full ASIL compliance (ASIL D systematic, up to ASIL C random)

- Four-way VLIW architecture combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector lengths

- 8, 16, and 32-bit integer SIMD engines

-

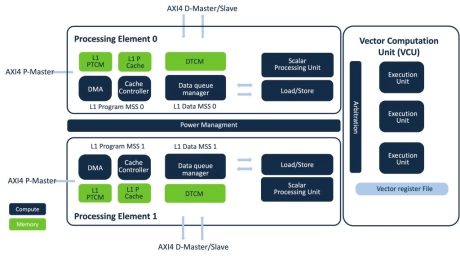

512-bit Vector DSP IP, Dual Core with Functional Safety

- Integrated hardware safety features with minimal area and power impact for full ASIL compliance (ASIL D systematic, up to ASIL C random)

- Four-way VLIW architecture combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector lengths

- 8, 16, and 32-bit integer SIMD engines

-

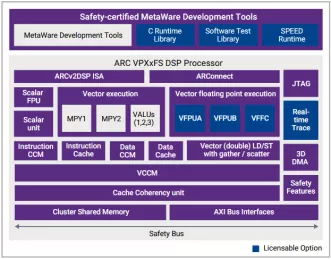

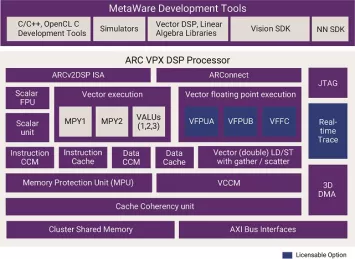

512-bit Vector DSP IP, Single Core

- Four-way VLIW combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector word lengths

- 8, 16, and 32-bit integer SIMD engines

- IEEE 754-compliant vector floating point unit option offers single-precision or half-precision operations and advanced math functions

-

512-bit Vector DSP IP, Quad Core

- Four-way VLIW combining scalar and vector operations

- 128-bit, 256-bit and 512-bit vector word lengths

- 8, 16, and 32-bit integer SIMD engines

- IEEE 754-compliant vector floating point unit option offers single-precision or half-precision operations and advanced math functions