Coprocessor IP

Filter

Compare

87

IP

from

30

vendors

(1

-

10)

-

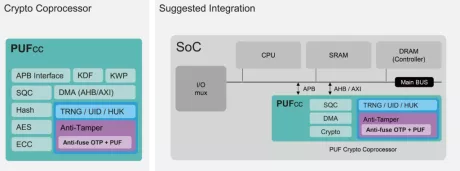

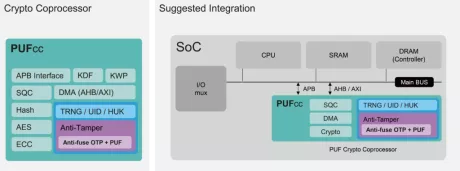

TLS 1.3 Compliant Crypto Coprocessor

- NIST CAVP certified and OSCCA standard compliant crypto engine suite

- Includes private/public key ciphers, message authentication code, hashes, and key derivation

- Key wrapping function for the secure export of keys

- Public-key coprocessor for digital signatures and key agreements over elliptic/Edward curves

-

Cryptographic co-processor for lightweight cryptography

- Support AES-XTS mode — IEEE Std 1619-2007 standard compliance

- Support 128 and 256-bit key size

- Random memory block access support

-

Crypto Coprocessor

- Comprehensively support all CPU architectures

- Crypto engine collective, consisting of private key cipher, message authentication code, hash, and key derivation functions that are NIST CAVP certified and OSCCA standards compliant

- Key wrapping function aiding the export of keys for external use

-

Vector Floating-point coprocessor based on ARM VFPv2 Instruction Set Architecture for FA626TE 32-bit RISC CPU

-

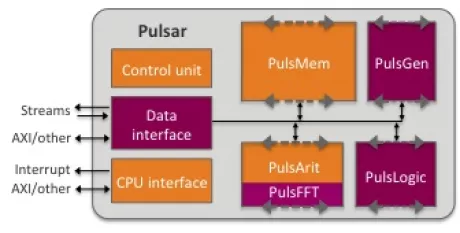

Scalable and Programmable Co-processor

- Hardware scalability to offer the best cost-performance trade-off

- Programmable Software-defined solution for flexible DSP components

- Enables complex DSP and high data-rate communication system design

- Can be optimized for FPGA and ASIC targets

-

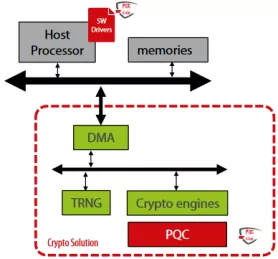

Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

- The Crypto Coprocessors are a hardware IP core platform that accelerates cryptographic operations in System-on-Chip (SoC) environment on FPGA or ASIC.

- Symmetric operations are offloaded very efficiently as it has a built-in scatter/gather DMA. The coprocessors can be used to accelerate/offload IPsec, VPN, TLS/SSL, disk encryption, or any custom application requiring cryptography algorithms.

-

Advanced Encryption Standard Cryptographic Co-Processor

- The DAES IP Core is a high-performance AES hardware accelerator designed to execute Advanced Encryption Standard (AES) operations with exceptional speed, reliability, and energy efficiency.

- Optimized for embedded systems, SoCs, FPGA designs, and other security-critical applications, the DAES IP Core significantly offloads computationally intensive AES tasks from the main processor, enhancing both system performance and power efficiency.

-

Public-Key Cryptography PKCS IP Core

- Comprehensive implementation in accordance with RSA Laboratories' Public-Key Cryptography Standards (PKCS) series, PKCS #5 v2.0

- Support for SHA256 algorithm

- Technology-independent HDL model

- Simple external interface for easy adaptation

-

ECDSA (Elliptic Curve Digital Signature) IP Core

- Full ECDSA implementation adhering to Standards for Efficient Cryptography (SEC)

- Bitcoin algorithm support

- Technology-independent HDL model

- Simple external interface for easy adaptation

-

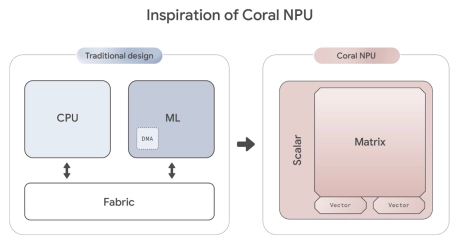

RISC-V-Based, Open Source AI Accelerator for the Edge

- Coral NPU is a machine learning (ML) accelerator core designed for energy-efficient AI at the edge.

- Based on the open hardware RISC-V ISA, it is available as validated open source IP, for commercial silicon integration.