Cadence PCIe IP

Filter

Compare

28

IP

from

2

vendors

(1

-

10)

-

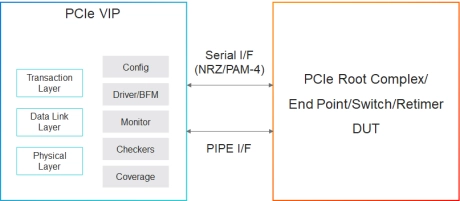

Simulation VIP for PCIe

- Device Type

- Root Complex, End Point, Legacy End Point, Switch, PHY DUT, Bridge

- Interface

- Serial, Parallel (8-bit, 10-bit, 128-bit, and 130-bit), PIE8, PIPE 3.0, PIPE 4.0, PIPE 4.3, PIPE 4.4.x, PIPE 5.x, PIPE 6.0

-

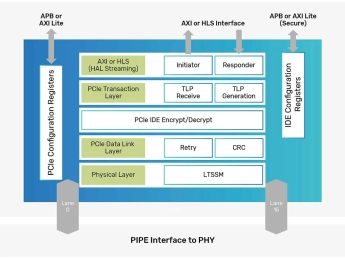

Controller for PCIe

- The Cadence Controller IP for PCIe is compliant with PCIe 6.0, 5.0, 4.0, 3.1, 2.1, 1.1 protocol versions and supports the latest ECNs including IDE/DOE so that applications can benefit from the latest updates to the specifications

- The controller IP is available as root-port, end-point, or dual-mode to allow for versatile use cases, and multifurcation support allows applications to build configurations that can support configurations from 1x16 to 16x1 easily

- The controller provides SR-IOV support with 256 functions and 4K payload size, scalable I/O virtualization with PASID is also available

-

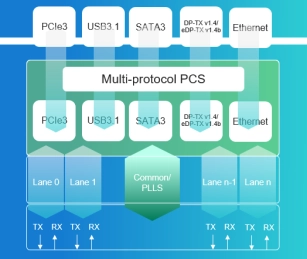

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

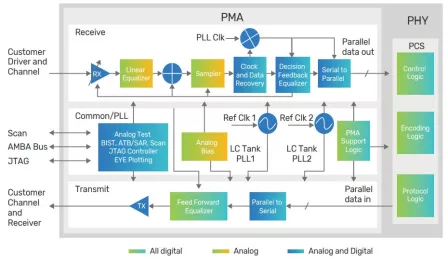

10Gbps Multi-Protocol PHY IP (+PCIe 3.1)

- Supports 10G-KR, PCIe 3.1/2.0/1.0, XAUI, Q/SGMII, and Gigabit Ethernet

- LC tank PLL with a wide range of reference clock frequencies and SSC

- High-performance decision feedback equalization and adaptive CTLE

- Serial and parallel loop-back functions

- Available in X1 through X10 lane configurations

-

PHY for PCIe 7.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

PHY for PCIe 6.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

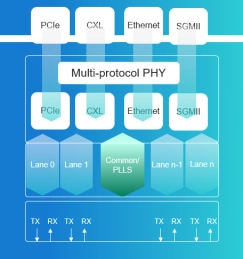

PHY for PCIe 5.0 and CXL

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Advanced equalization and clock-data-recovery to deliver unmatched channel loss handling performance and reliability

- Eye Surf —provides convenient access to an integrated non-destructive real-time eye scope and BER bathtub curve to monitor the bit error rate (BER) and the link performance during live traffic

-

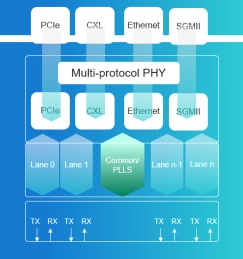

PHY for PCIe 4.0 - Low-power, long-reach, multi-protocol PHY for PCIe 4.0

- Wide range of protocols that support networking, high-performance computing (HPC), and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- User-friendly graphical interface provides easy access to embedded bit-error-rate (BER) and pattern testers and monitors to measure the link performance in real time

-

PCIe 4/3/2 SerDes PHY - GLOBALFOUNDRIES 22nm

- Duplex lane configurations of x2, x4, and x35

- Transmit swing of at least 800mV differential peak-to-peak for MR & LR, 360mv for SR

- Support for AC-coupled interfaces

- Fine-grain power up/down capability for power optimization, and ability to turn off unused link(s)

-

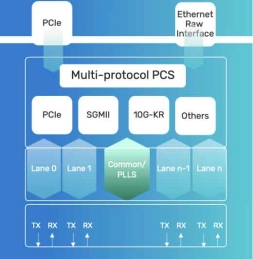

10Gbps Multi-Link and Multi-Protocol PCIe 4.0 PHY IP for SMIC

- Supports USB 3.1, PCIe 3.0/2.0/1.0, DP-TX v1.4/ eDP-TX v1.4b, SATA 3, QSGMII,and SGMII

- Supports PCIe L1 sub-states

- Supports SRIS and internal SSC generation

- Multi-protocol support for simultaneous independent links