Cadence DSP IP

Filter

Compare

30

IP

from

4

vendors

(1

-

10)

-

Tensilica Vision P1 DSP

- 256/128b Load/Store capabilities

- 128 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing

-

Tensilica Vision P6 DSP

- 1024/512b Load/Store capabilities

- 256 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing

-

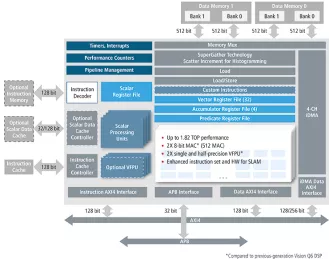

Tensilica Vision Q8 DSP

- 2048/1024b Load/Store capabilities

- 1024 8-bit MAC: 2X MAC capability versus Vision Q7 DSP

- 8/16/32-bit fixed-point processing

- Double-precision (FP64), single-precision (FP32), and half-precision (FP16) floating-point processing

-

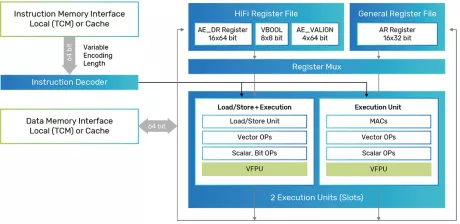

Tensilica HiFi 3z DSP

- Flexible VLIW Bundle Instruction sizes

- Up to 2 times more16x16 MACs compared to HiFi 3 DSP

- On average 20% performance boost over HiFi 3 DSP

-

Tensilica HiFi 4 DSP

- Support for eight 32x16-bit MACs per cycle under specific conditions

- Four very long instruction word (VLIW) slot architecture capable of issuing two 64-bit loads per cycle

- Optional vector floating-point unit available, providing up to four single-precision IEEE floating-point MACs per cycle

- Software compatibility with the complete HiFi DSP product line, totaling over 300 HiFi-optimized audio and voice codecs and audio enhancement software packages

-

Tensilica HiFi 1 DSP

- Cycle and energy efficient for Bluetooth and Bluetooth Low Energy (BLE) codecs for speech and music

- Efficient neural network acceleration ISA and architecture support

-

Tensilica Vision Q7 DSP

- Doubles Vision and AI Performance for Automotive, AR/VR, Mobile and Surveillance Markets

-

Tensilica HiFi 5 DSP

- Five very long instruction word (VLIW)-slot architecture capable of issuing two 128-bit loads per cycle

-

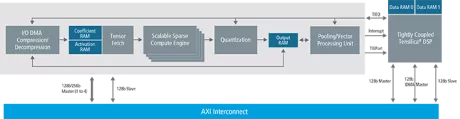

Tensilica Fusion F1 DSP

- Specialized design to take advantage of sparsity in weights and activations for compute and bandwidth reduction