CXL 2.0 IP

Filter

Compare

103

IP

from

17

vendors

(1

-

10)

-

CXL 2.0 Premium Controller Device/Host/DM 512b with AMBA bridge and Advanced HPC Features (Arm CCA)

- Supports all required features of CXL 3.1 and CXL 3.0

- Supports all key features and performance requirements in the CXL 3.0, 2.0, 1.1 and 1.0 specifications

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

-

CXL 2.0 Premium Controller Device/Host/DM 512b with AMBA bridge + LTI and MSI-GIC interfaces

- Supports all required features of CXL 3.1 and CXL 3.0

- Supports all key features and performance requirements in the CXL 3.0, 2.0, 1.1 and 1.0 specifications

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

-

CXL 2.0 Premium Controller Device/Host/DM 512b with AMBA bridge

- Supports all required features of CXL 3.1 and CXL 3.0

- Supports all key features and performance requirements in the CXL 3.0, 2.0, 1.1 and 1.0 specifications

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

-

CXL 2.0 Premium Controller Device/Host/DM 512b

- Supports all required features of CXL 3.1 and CXL 3.0

- Supports all key features and performance requirements in the CXL 3.0, 2.0, 1.1 and 1.0 specifications

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

-

CXL 2.0 Retimer

- Compliant with CXL 2.0 spec.

- Compliant with PCIE Gen5/4 Specs.

- Forward mode supported.

- X1,X2,X4,X8,X16 lanes supported.

-

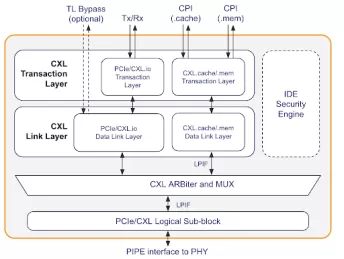

CXL 2.0 Integrity and Data Encryption Security Module

- Compliant with the CXL 2.0 IDE specifications for CXL.cache/mem

- Compliant with PCI Express IDE specification for CXL.io

- High-performance AES-GCM based packet encryption, decryption, authentication

-

CXL 2.0 Dual Mode Controller

- Compatible with CXL 2.0 specification and backward compatible with CXL V1.0 and CXL V1.1

-

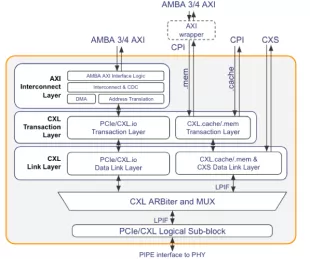

CXL 2.0 Controller with AXI

- Internal data path size automatically scales up or down (256-, 512- bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

-

CXL 2.0 Controller

- Internal data path size automatically scales up or down (256, 512 bits) based on max. link speed and width for reduced gate count and optimal throughput

- Dynamically adjustable application layer frequency down to 8Mhz for increased power savings

- Optional MSI/MSI-X register remapping to memory for reduced gate count when SR-IOV is implemented

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs (when supported)

-

Supports all key features and performance requirements in the CXL 3.0, 2.0, 1.1 and 1.0 specifications

- Supports key required features of the CXL 3.0 specification and full backwards compatibility with CXL 2.0, 1.0 and 1.1

- Supports PCIe 6.0 mode with 64 GT/s and x16 link width

- CXL license includes PCIe 6.0 functionality and fallback mode

- Customers using CXL do not need an additional PCIe 6.0 license