CAN transceiver IP

Filter

Compare

255

IP

from

67

vendors

(1

-

10)

-

3.3V CAN Transceiver

- The TS_CAN_3V3_X8 is a 3.3V CAN transceiver, which supports data rates up to 1Mbps and is compatible with ISO 11898-2 compliant CAN transceivers.

- It supports a standby mode with wake up via wake-up pattern.

- The TS_CAN_3V3_X8 provides a symmetrical output signal on CANL/CANH and incorporates slope-control to improve EMI performance.

-

CAN Transceiver

- High Speed Baudrate up to 1Mbaud

- Compliant to ISO 11898-5

- XFAB 0.35µm process: XH035

- Very low EME and very high EMI

-

Controller Area Network with Flexible Data rate

- The XKAN module is a communication controller implementing the CAN protocol specification version 2.0 part A, B and CAN with Flexible Data-Rate protocol specification version 1.0.

- There is a 8Kbyte ram in XKAN subsystem, the ram implements filters for accept CAN base format (2.0 A) and extended format (2.0 B), receive buffers and transmit buffers.

-

Protocol controller IP for a CAN FD light responder node

- The FDLR_CAN is a CAN IP module that can be implemented in an ASIC, FPGA, and mixed-signal device.

- It supports CAN FD light responder communication according to ISO 11898-1:2024.

-

Protocol controller IP for Classical CAN / CAN FD / CAN FD light commander and CAN XL

- The XS_CAN is a low gate count CAN IP module that can be realized as stand-alone device, as part of an SoC, as part of an ASIC, or on an FPGA.

- Safety Element out of Context (SEooC) according to ISO 26262-11:2018 Clause.Developed according to the automotive cybersecurity standard ISO 21434.

-

High Performance Transceiver

- Our FD-TRx Series is a transceiver comprising both of our breakthrough flagship FDDAC and FDADC technologies in a single chip offering a full solution for bi-directional connectivity.

- Its ultra-wide coherent modulation bandwidth and low energy consumption make it ideally suited for wide bandwidth applications such as mmWave-WiFi, mmWave5G and 6G, radar, or satellite.

-

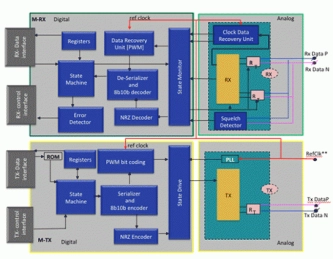

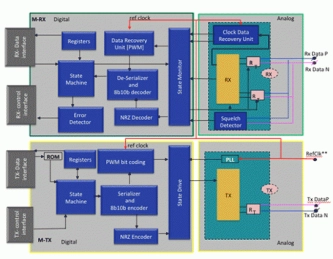

MIPI M-PHY® 3.1 Analog Transceiver

- The M-PHYs are of Type 1, which apply to UFS, LLI and CSI-3 protocols.

- The Multi-gear M-PHY 3.0 consists of analog transceivers, high speed PLL, data recovery units as well as the state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant to the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

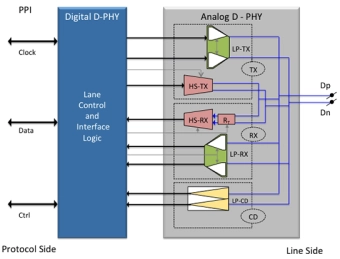

MIPI D-PHY Analog Transceiver IP Core

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

MIPI M-PHY® 4.1 Analog Transceiver

- The M-PHY is of Type 1, which apply to UFS, LLI, and CSI-3 protocols. The Multi-gear M-PHY 4.1 consists of analog transceivers, high-speed PLL, data recovery units as well as state-machine control — all in a single GDSII.

- The interface to the link protocol-specific controller (host or device) is compliant with the M-PHY RMMI specification, which allows seamless integration of the two IPs, namely the controller and the PHY, into the chip design.

-

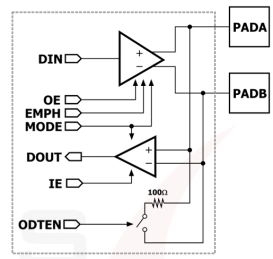

2Gbps LVDS/SVLS Combo Transceiver in TSMC 16nm

- AD_SLVS_LVDS is a highly configurable 2Gbps transceiver for LVDS or SLVS interfaces. With features like dynamic interface selection, on-die termination and pre-emphasis, this I/O is flexible enough for any system.

- To compliment this I/O, the vendor also offers a accompanying silicon-proven ESD and GPIO pad library in TSMC 12/16nm.

- This I/O provides 2kV HBM protection but can be extended up to 8kV upon request.