Automotive RISC-V IP

Filter

Compare

26

IP

from

14

vendors

(1

-

10)

-

Data Movement Engine - Best in class multi-core high-performance AI-enabled RISC-V Automotive CPU for ADAS, AVs and SDVs

- The only Multi-Threaded Out-of-Order RISC-V Core with ASIL-B Certification

- Highly scalable multi-core, multi-cluster, coherent computing solution

- MIPS extensions for improved performance and functionality

- Use in Automotive, Datacenter, and Embedded applications

-

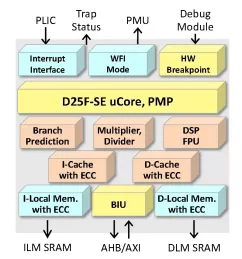

32-bit RISC-V processor specifically designed for the Automotive and Functional Safety markets

- 32-bit RISC-V ISA

- ASIL B and ASIL D area optimised product variants

- Functional Safety Package and Independent Assessment

-

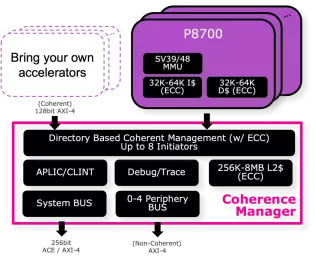

Scalable RISC-V CPUs for Data Center, Automotive, and Intelligent Edge

- 11+ SPECint2017 (rate=1) at up to 4.2 GHz

- Enhanced RISC-V standard matrix extension support alongside RVV 1.0 and scalar compute

- 24 TeraFLOPS/core of FP8 matrix compute for AI/ML acceleration, or up to 4.5 PFLOPS in a 192-core chiplet-based SiP

- Significantly higher IPC and performance-per-watt, driven by new microarchitecture innovations

-

RISC-V CPU IP With ISO 26262 Automotive Functional Safety Compliant

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- Bit-manipulation extensions

-

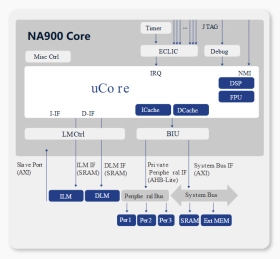

32-Bit Automotive Processor - 9-Stage Pipeline, Dual-issue

- NA900 series processor is the 1st ISO26262 ASIL-B/D Product Certified RISC-V CPU IP, Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

32-Bit Automotive Processor - 3-Stage Pipeline, Single/Dual-issue

- NA300 series processor is a ISO26262 ASIL-B/D Certified RISC-V CPU IP,Nuclei self-developed STL supports multiple ASIL-B automotive use cases.

-

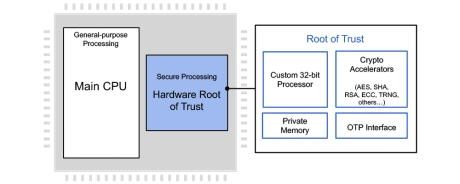

Embedded Hardware Security Module (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- The RT-64x Embedded Hardware Security Module (Root of Trust) family are fully programmable, ISO 26262 ASIL-B hardware security cores offering security by design for automotive applications.

- They protect against a wide range of failures such as permanent, transient and latent faults and hardware and software attacks with state-of-the-art anti-tamper and security techniques.

-

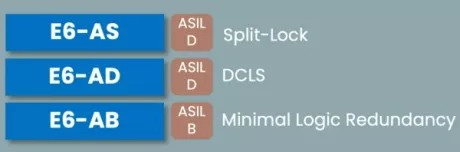

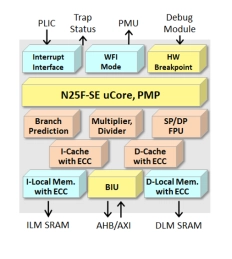

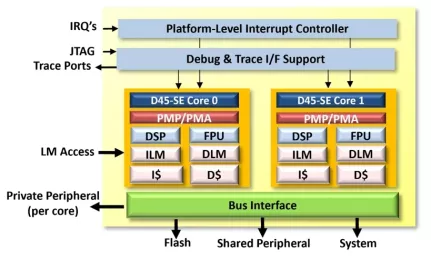

8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- The 32-bit D45-SE is an 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications.

-

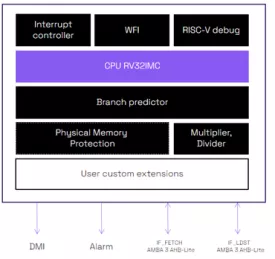

32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Flexible use cases

- roven technology

- State-of-the-art safety and security

-

32-bit CPU IP core - ISO 26262 Automotive Functional Safety Compliant

- 32-bit CPU IP core that supports ISO 26262 ASIL B level functional safety for automotive applications