Acceleration Engine IP

Filter

Compare

102

IP

from

36

vendors

(1

-

10)

-

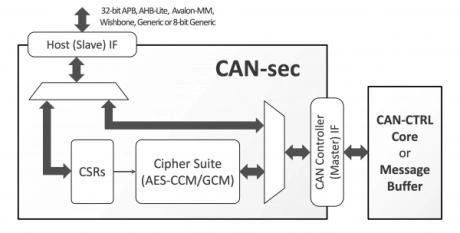

CANsec Acceleration Engine

- The CAN-SEC IP core implements a hardware accelerator for the CANsec extension of the CAN-XL protocol, as defined in CiA’s 613-2 specification.

- The CANsec specification provisions two ciphers with key lengths of 128, 192, or 256 bits to protect CAN XL frames’ payload, all of which are supported by the hardware accelerator.

-

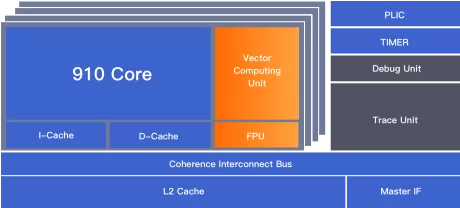

High-performance 64-bit RISC-V architecture multi-core processor with AI vector acceleration engine

- Instruction set: RISC-V RV64GC/RV 64GCV;

- Multi-core: Isomorphic multi-core with 1 to 4 optional clusters. Each cluster can have 1 to 4 optional cores;

-

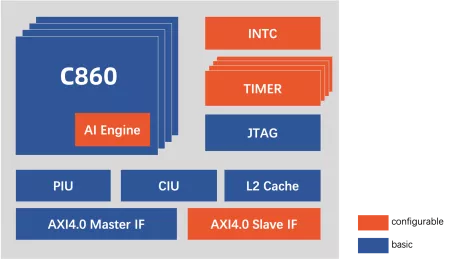

High-performance 32-bit multi-core processor with AI acceleration engine

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Multi-core: Isomorphic multi-core, with 1 to 4 optional cores;

- Pipeline: 12-stage;

- Microarchitecture: Tri-issue, deep out-of-order;

-

ML-KEM Key Encapsulation & ML-DSA Digital Signature Engine

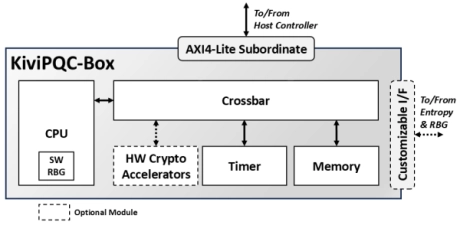

- The KiviPQC™-Box is a hardware accelerator for post-quantum cryptographic operations.

- It implements both the Module Lattice-based Key Encapsulation Mechanism (ML-KEM) and the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 203 and FIPS 204, respectively.

-

ML-DSA Digital Signature Engine

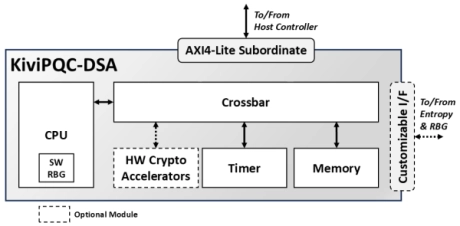

- The KiviPQC™-DSA is a hardware accelerator for post-quantum cryptographic operations.

- It implements the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 204.

- This mechanism realizes the appropriate procedures for securely generating a private/public key pair, digitally signing a message or a data block, and performing digital signature verification.

-

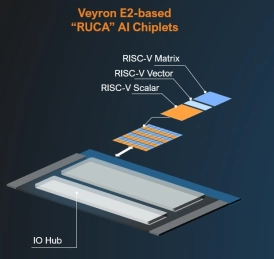

RISC-V AI Acceleration Platform - Scalable, standards-aligned soft chiplet IP

- Built on RISC-V and delivered as soft chiplet IP, the Veyron E2X provides scalable, standards-based AI acceleration that customers can integrate and customize freely.

-

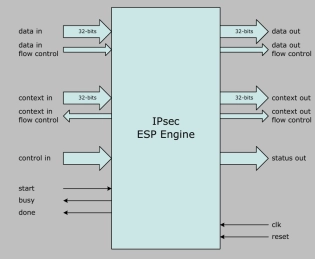

IPsec ESP IP core for FPGA

- Built on the success of Helion's industry proven cryptographic IP cores, the Helion ESP Engine provides hardware acceleration of the key cryptographic algorithms and packet processing required by the IPsec Encapsulating Security Payload (ESP) protocol.

- Its modular architecture provides the flexibility to support only those cryptographic algorithms required for a particular application to provide the optimum logic area and performance trade-off.

-

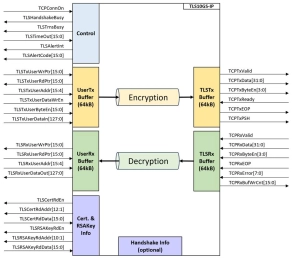

CPU-less TLS1.3 Offload IP core for FPGA Acceleration

- TLS1.3 IP (Transport Layer Security IP) is the CPU-less & High-performance TLS v1.3 protocol engine for FPGA Acceleration with no CPU and external memory required.

- Providing maximum Gigabit Ethernet throughput for highly secure data transmission over 1G/10G/25G/100G network. Protect your valuable data from potential security breaches by using TLS secure transmission now

-

100G bps Full TCP & UDP Offload Engine

- Increase your TCP and UDP Network actual performance by up to 600%

- Built around Proven and Mature TCP and UDP technology since 2009.

- 40G: In production. Performed Live demo of 40G at Super Computing 2015

- Qualified on Altera/Intel and Xilinx. FPGA Subsystems Solutions available now

- First company to implement and deliver Full TCP Stack in High performance FPGA in 2009.

-

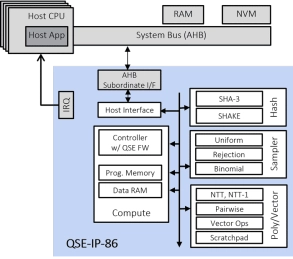

Fast Quantum Safe Engine for ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium)

- The Quantum Safe Engine (QSE) IP provides Quantum Safe Cryptography acceleration for ASIC, SoC and FPGA devices.

- The QSE-IP-86 core is typically integrated in a hardware Root of Trust or embedded secure element in chip designs together with a PKE-IP-85 core that accelerates classic public key cryptography and a TRNG-IP-76 core that generates true random numbers.