ASIL-B IP

Filter

Compare

292

IP

from

18

vendors

(1

-

10)

-

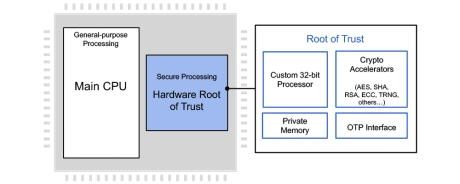

Embedded Hardware Security Module (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- The RT-64x Embedded Hardware Security Module (Root of Trust) family are fully programmable, ISO 26262 ASIL-B hardware security cores offering security by design for automotive applications.

- They protect against a wide range of failures such as permanent, transient and latent faults and hardware and software attacks with state-of-the-art anti-tamper and security techniques.

-

MIPI DPHY_RX v1.2, 1C2D, TSMC 16FFC, E/W orientation (ASIL-B)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

MIPI DPHY_RX v1.2, 2C4D, TSMC 16FFC, E/W orientation (ASIL-B)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

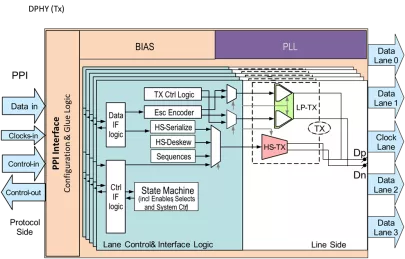

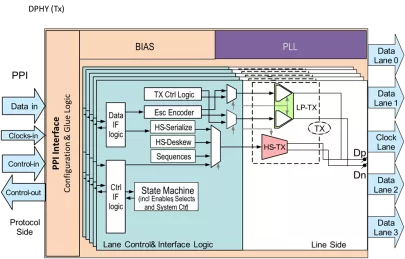

MIPI DPHY_TX v1.2, 1C2D, TSMC 16FFC, E/W orientation (ASIL-B)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

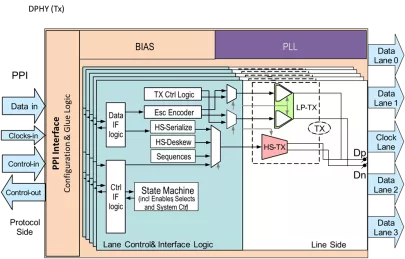

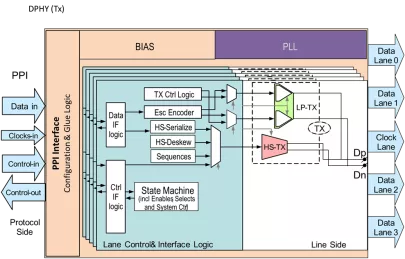

MIPI DPHY_TX v1.2, 1C4D, TSMC 16FFC, E/W orientation (ASIL-B)

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

-

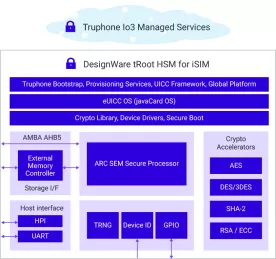

tRoot V023 FS Hardware Secure Module, ASIL-B compliant (w/ ARC EM22FS)

- ASIL B Certified tRoot Hardware Secure Module provides the Root of Trust for a system, protects against malicious attacks, and prevents random and systematic faults

- Meets stringent ISO 26262 safety process and documentation requirements (ASIL D systematic grade)

- Fully programmable solution safeguards against evolving threats with high-grade security

-

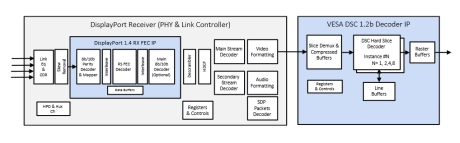

DisplayPort 1.4 FEC Transmitter (Tx) ASIL-B

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

-

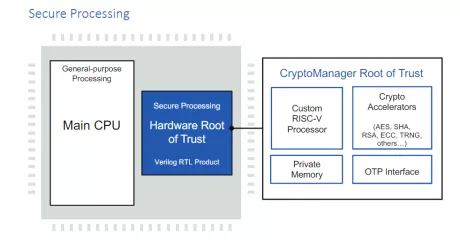

Embedded HSM Family (Root of Trust) - Automotive Grade ISO 26262 ASIL-B

- Custom-designed 32-bit RISC-V secure processor

- Security model include hierarchical privilege model, secure key management policy, hardware-enforced isolation/access control/protection, error management policy

- Standard hardware cryptographic accelerators, including AES (all modes), HMAC, SHA-2 (all modes), RSA up to 4096 bits, ECC up to 521 bits, a NIST-compliant Random Bit Generator, AXI Multi Issue Out-of-Order, and Fast DMA capability. Additional algorithms such as Whirlpool (SHE), SHA-1 (legacy), AES-CMAC, SHA-3, Poly1305, ChaCha and OSCCA SM2-3-4 are available

- Multi-layered security model protects all core components against a wide range of attacks

-

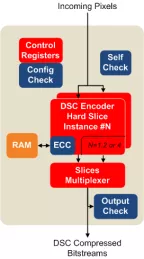

VESA DSC 1.1 Encoder IP Core for Automotive Displays (ASIL-B Ready ISO 26262 Certified)

- VESA DSC 1.1 compliant

- Supports all DSC 1.1 mandatory encoding mechanisms

- Configurable maximum display resolution

-

CAN 2.0, CAN FD - Developed as ISO26262-10 Safety Element out of Context (ISO26262 soft IP SEooC, ASIL-B ready design)

- Designed in accordance to ISO 11898-1:2015

- Supports CAN 2.0B and CAN FD frames

- Support up to 64 bytes data frames