ARM Cortex-M IP

Filter

Compare

25

IP

from

8

vendors

(1

-

10)

-

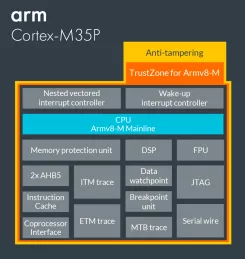

Tamper-resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M

- Tamper-resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M

-

Arm Cortex-M52 Processor

- Smallest Area, Energy-Efficient Processor for AIoT

- Simplify Software Development

- Faster Route to Security Certification

-

Arm Cortex-M55 Processor

- Improve ML and DSP Performance

- Accelerate Time to Market

- Simplify Software Development

-

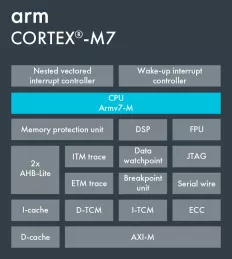

Arm Cortex-M7

- Optional instruction and data TCMs up to 16MB - Fast access to critical code and data via a dedicated bus. Increases responsiveness to critical events.

- Harvard instruction cache and data cache on 64-bit AMBA 4 AXI interface - Optimises access to large external memories or slow peripherals, reducing latency. Instruction and data caches are optional and separately configurable from 4KB to 64KB.

- SIMD, saturating arithmetic, fast MAC - Powerful instruction set for accelerating DSP applications, built right into the processor. A highly optimised DSP library built using these instructions is available free-of-charge from the Arm website.

- Powerful debug and non-obtrusive real-time trace, with optional full data trace - Comprehensive debug and trace features dramatically improve developer productivity. It is extremely efficient to develop embedded software with proper debug.

-

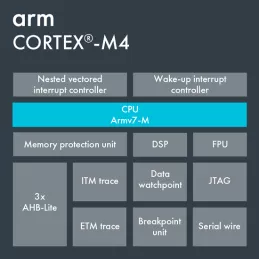

Arm Cortex-M4

- SIMD, saturating arithmetic, fast MAC - Powerful instruction set for accelerating DSP applications, built right into the processor. A highly optimised DSP library built using these instructions is available free-of-charge from the Arm website.

- Powerful debug and non-obtrusive real-time trace - Comprehensive debug and trace features dramatically improve developer productivity. It is extremely efficient to develop embedded software with proper debug.

- Memory Protection Unit (MPU) - Software reliability improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data.

- Integrated nested vectored interrupt controller (NVIC) - There is no need for a standalone external interrupt controller. Interrupt handling is taken care of by the NVIC removing the complexity of managing interrupts manually via the processor.

-

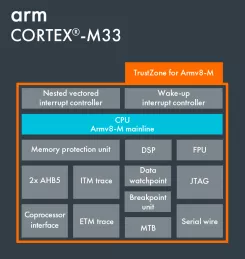

Arm Cortex-M33

- TrustZone for Armv8-M - A foundation for security for embedded devices. TrustZone offers software isolation to code, memory and I/O while retaining the requirements of embedded applications: real-time deterministic response, minimal switching overhead, and ease of software development.

- Co-processor interface - A dedicated bus for extending the operation of the processor with tightly coupled co-processors to handle frequent and compute intensive operations in an ecosystem friendly manner. The interface supports up to eight accelerators and takes into account the security state of the co-processor.

- SIMD, saturating arithmetic, fast MAC - Powerful instruction set for accelerating DSP applications, built right into the processor. A highly optimized DSP library built using these instructions is available free-of-charge from the Arm website (CMSIS Library).

- Memory Protection Unit (MPU) - Software reliability and system security improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data. Each of the security zones can have a dedicated MPU that may be configured with a different number of regions.

-

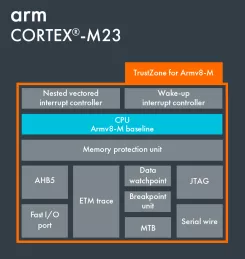

Arm Cortex-M23

- TrustZone for Armv8-M - A foundation for security for embedded devices. TrustZone offers software isolation to code, memory and I/O while retaining the requirements of embedded applications: real-time deterministic response, minimal switching overhead, and ease of software development.

- Energy efficient two-stage pipeline processor - The smallest of Arm processors with TrustZone technology. Brings compactness and energy efficiency while providing support for the full Armv8-M baseline instruction set.

- Memory Protection Unit (MPU) - Software reliability improves when each module is allowed access to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data. Each security zone can have a dedicated MPU.

- ntegrated Nested Vectored Interrupt Controller (NVIC) - There is no need for a standalone external interrupt controller. Interrupt handling is taken care of by the NVIC removing the complexity of managing interrupts manually via the processor.

-

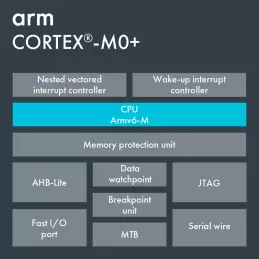

Arm Cortex-M0+

- Memory protection unit - Software reliability improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data.

- Binary upward compatible with all other Cortex-M processors - The Cortex-M0+ has mainly 16bit Thumb-2 instructions and few 32bit ones. These instructions are also present on all the other Cortex-M processors. Hence all code written for the Cortex-M0+ will run as is on the other processors.

- Built-in low-power features - Sleep, deep sleep and state retention are three low power modes available to the user.

- Optional Debug Access Port and Serial Wire Debug - For devices where every pin counts the serial wire debug port uses only two pins.

-

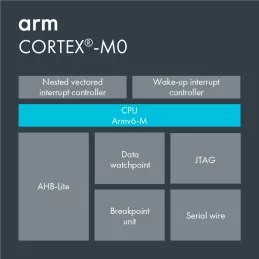

Small, Low Power, Energy Efficient 32-bit Microcontroller Processor

- Exceptional code density - on average, the mix between 16-bit and 32-bit instructions yields a better code density when compared to 8-bit and 16-bit architectures. This has significant advantages in terms of reduced memory requirements and maximizing the usage of precious on-chip Flash memory.

- Binary upward compatible with all other Cortex-M processors - the Cortex-M0 has mainly 16-bit Thumb-2 instructions and few 32-bit ones. These instructions are also present on all the other Cortex-M processors. Hence all code written for the Cortex-M0 will run as is on the other processors.

- Built-in low-power features - sleep, deep sleep and state retention are three low power modes available to the user

- Optional Debug Access Port and Serial Wire Debug - for devices where every pin counts the serial wire debug port uses only two pins

-

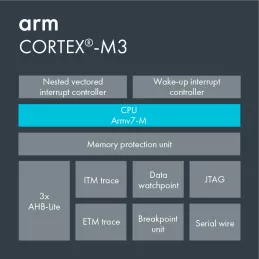

32-bit RISC Processor To Deliver High Performance In Low-Cost Microcontroller Applications

- Powerful debug and non-intrusive real-time trace - Comprehensive debug and trace features dramatically improve developer productivity. It is extremely efficient to develop embedded software with proper debug.

- Memory Protection Unit (MPU) - Software reliability improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data.

- Integrated nested vectored interrupt controller (NVIC) - There is no need for a standalone external interrupt controller. Interrupt handling is taken care of by the NVIC removing the complexity of managing interrupts manually via the processor.

- Thumb-2 code density - On average, the mix between 16bit and 32bit instructions yields a better code density when compared to 8bit and 16bit architectures. This has significant advantages in terms of reduced memory requirements and maximizing the usage of precious on-chip Flash memory.