ARC HS4xD IP

Filter

Compare

9

IP

from

1

vendors

(1

-

9)

-

DSP-enhanced ARC EMxD and HS4xD processors provide combined RISC + DSP processing for computation intensive applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.

-

ARC EM9D 32-bit DSP Enhanced Processor core based on the ARCv2DSP ISA with CCM and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

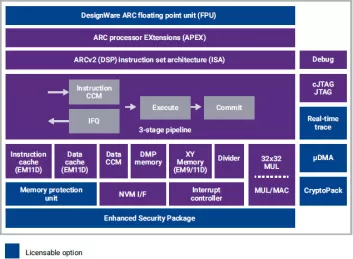

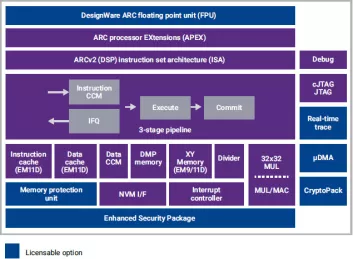

ARC EM11D Enhanced 32-bit processor core, ARCv2DSP ISA with Cache and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

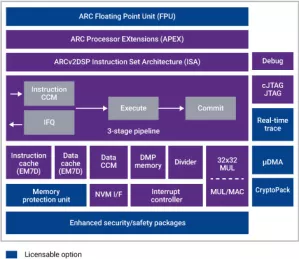

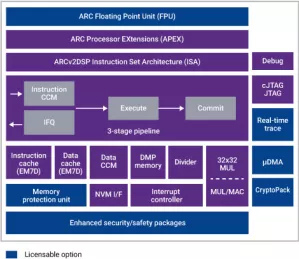

ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC EM5D Enhanced 32-bit processor core, ARCv2DSP ISA, for low power embedded DSP applications

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC HS47Dx4 quad-core version of dual-issue HS47D ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC HS47Dx2 dual-core version of dual-issue HS47D ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

ARC HS47D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

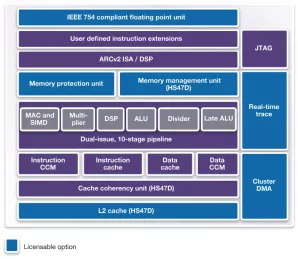

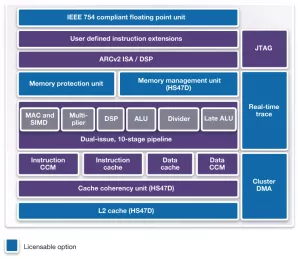

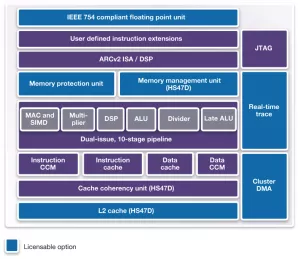

Optimized for GHz+ operating speeds with minimum area and power consumption, ARC HS Processors are ideal for very high-performance embedded applications

- ARC processor cores are optimized to deliver the best performance/power/area (PPA) efficiency in the industry for embedded SoCs. Designed from the start for power-sensitive embedded applications, ARC processors implement a Harvard architecture for higher performance through simultaneous instruction and data memory access, and a high-speed scalar pipeline for maximum power efficiency. The 32-bit RISC engine offers a mixed 16-bit/32-bit instruction set for greater code density in embedded systems.

- ARC's high degree of configurability and instruction set architecture (ISA) extensibility contribute to its best-in-class PPA efficiency. Designers have the ability to add or omit hardware features to optimize the core's PPA for their target application - no wasted gates. ARC users also have the ability to add their own custom instructions and hardware accelerators to the core, as well as tightly couple memory and peripherals, enabling dramatic improvements in performance and power-efficiency at both the processor and system levels.

- Complete and proven commercial and open source tool chains, optimized for ARC processors, give SoC designers the development environment they need to efficiently develop ARC-based systems that meet all of their PPA targets.