AHB IP

Filter

Compare

757

IP

from

73

vendors

(1

-

10)

-

Verification IP for AMBA AHB

- Complete protocol support for AHB5, AHB3, AHB2, AHB-Lite, and AHB Multi Layer

- Includes primary, secondary, monitor

- Configurable bus model

- Backdoor access to AHB secondary memory

-

Parallel to AHB bridge, following AMBA4 specifications

- dos_parallel_AHB_bridge is a Parallel to AHB bridge, following AMBA4 specifications

-

I2S to AHB bridge, following AMBA4 specifications

- dos_I2S_AHB_bridge is an I2S to AHB bridge, following AMBA4 specifications

-

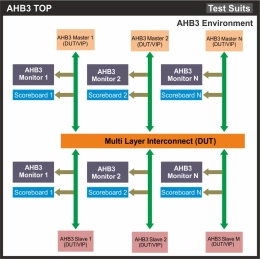

AMBA AHB 3 Lite Verification IP

- The AMBA 3 AHB-Lite Verification IP provides an effective & efficient way to verify the components interfacing with AMBA®3 AHB-Lite bus of an IP or SoC.

- The AMBA 3 AHB-Lite VIP is fully compliant with standard AMBA 3 AHB-Lite specification from ARM.

- This VIP is a light weight VIP with easy plug-andplay interface so that there is no hit on the design cycle time.

-

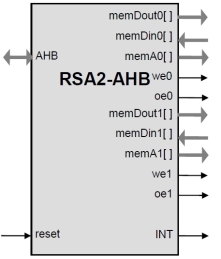

RSA2-AHB Accelerator Core with AHB Interface

- The core implements the exponentiation operation of the RSA cryptography Q = Pk.

- The operands for the exponentiation: k and P as well as the modulus are programmed into the memory and the calculation is started.

- Once the operation is complete, the result Q can be read through the AHB interface.

-

I²C to AHB Bridge

- The I²C slave to AHB bridge core is a I²C slave that provides a link between the I²C bus and AMBA AHB.

- The core is compatible with the Philips I²C standard.

-

SPI to AHB Bridge

- The SPI to AHB bridge is an SPI slave that provides a link between a SPI bus (that consists of two data signals, one clock signal and one select signal) and AMBA AHB.

- On the SPI bus the slave acts as an SPI memory device where accesses to the slave are translated to AMBA accesses.

- The core can translate SPI accesses to AMBA byte, half-word or word accesses. The access size to use is configurable via the SPI bus.

-

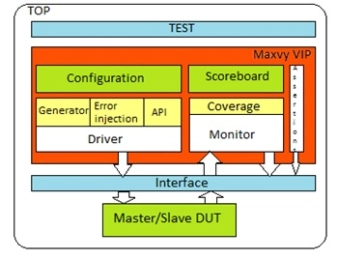

AHB Lite Verification IP

- The AHB Verification IP provides a complete solution for Verification of AMBA 3.0 AHB-Lite protocol v1.0 component of a SOC or ASIC

- The AHB-Lite Verification IP is fully compliant with standard AMBA 3 AHB-Lite Specification

- AMBA 3.0 AHB-Lite VIP is supported natively in SystemVerilog and UVM

-

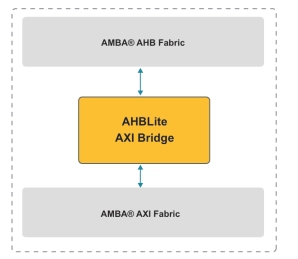

AHB Lite to AXI Bridge

- The AHB Lite to AXI Bridge translates an AHB Lite bus transaction (read or write) to an AXI bus transaction.

- It is expected that the AXI clock and the AHB clock are derived from the same clock source, and that the period of the AHB Lite clock is an integer multiple of the AXI clock in the range [1,16].

-

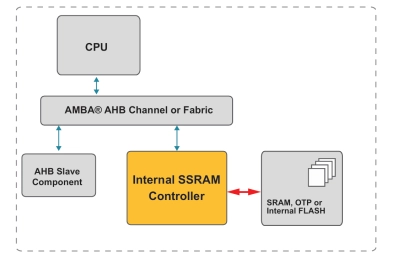

AHB SRAM Controller

- The AHB SRAM Controller provides a standard AHB interface to translate AHB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

- The AHB SRAM Controller provides zero-wait-state AHB access to the synchronous SRAM in all cases except for the following back-toback events: an AHB write directly followed by an AHB read.