64 Bit CPU IP

Filter

Compare

27

IP

from

15

vendors

(1

-

10)

-

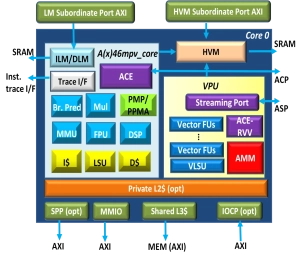

64 bit RISC-V Multicore Processor with 2048-bit VLEN and AMM

- 2 different packages with or without vector: AX46MPV, AX46MP

- in-order dual-issue 8-stage CPU core with up to 2048-bit VLEN

- Symmetric multiprocessing up to 16 cores

- Private Level-2 cache

- Shared L3 cache and coherence support

-

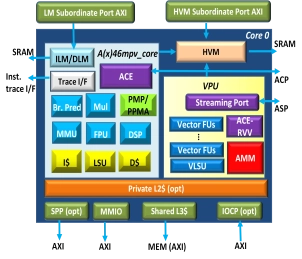

32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM

- AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension.

- It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

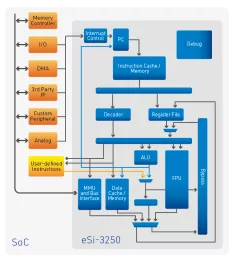

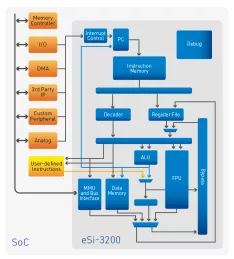

High-performance 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

-

Compact, low-power 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

- Optional IEEE 754 floating point unit (FPU)

-

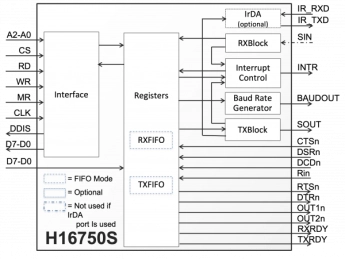

UART with FIFOs, IrDA and Synchronous CPU Interface

- Capable of running all existing 16450 and 16550a software

- Fully Synchronous design. All inputs and outputs are based on the rising edge of clock

- In FIFO mode, transmitter and receiver are each buffered with up to 256 byte FIFO’s to reduce the number of interrupts presented to the CPU

- Available with FIFO sizes of 8, 16, 32, 64, 128 or 256 bytes

-

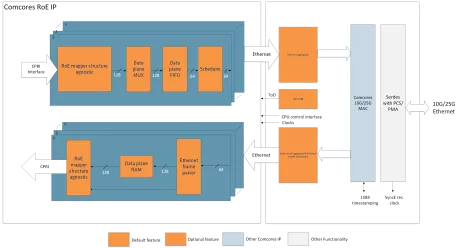

Radio over Ethernet (RoE)

- Complies with IEEE 1914.3 standard

- Supports multiple streams of CPRI and Ethernet

- Complies with CPRI 7.0 standard

-

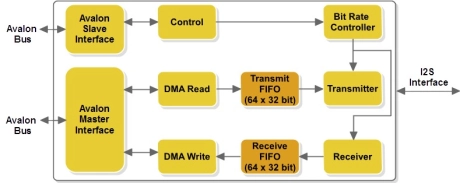

I2S Controller

- I²S Controller is designed to transfer audio data to and from Audio codec.

- It can be configured as both Master and Slave mode using software.

- The I²S IP is Phillips Inter IC Sound (I²S) specification compliant core for Altera devices.

-

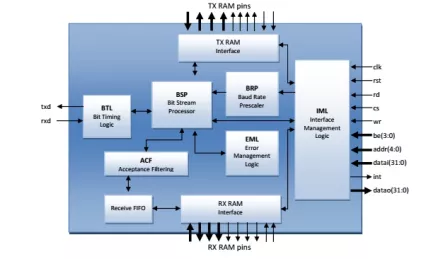

CAN 2.0 & CAN FD Bus Controller IP

- Conforms to Bosch CAN 2.0B Active

- 8/16/32-bit CPU slave interface with little or big endianess

- Simple interface allows easy connection to CPU

- Data rate up to 1 Mbps

-

Configurable CAN Bus Controller

- Conforms to Bosch CAN 2.0B Active

- 8/16/32-bit CPU slave interface with small or big endianness

- Simple interface allows easy connection to CPU

- Supports both standard (11-bit identifier) and extended (29 bit identifier) frames

-

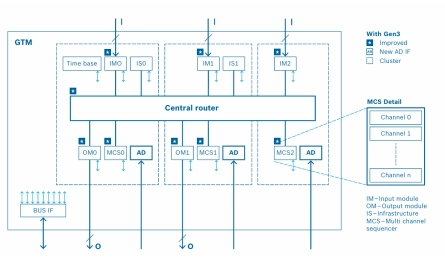

Generic timer IP

- Enables real-time control loops

- Deterministic multi-threaded architecture (8 threads per RISC unit)

- Programmability (special purpose RISC/ALU)

- Scalable and configurable architecture