4K/ 8K LCEVC Video Encoder IP

Filter

Compare

82

IP

from

23

vendors

(1

-

10)

-

Single-core video encoder - AV1, HEVC, AVC

- YUV420/YUV422/YUV444

- 8/10-bit depth

- I/P/B-frame

- Frame buffer compression

- Multi-instances

-

H.265/HEVC 422 10bit Encoder for 4K

- Compliant with ITU-T H.265, ISO/IEC 23008-2

- Main / Main 12 Profile Level 1 to 6.1

- Input format: Annex. B

-

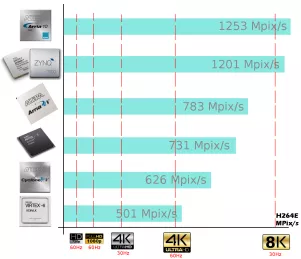

H.264 Encoder High Profile (8K on Zynq/Arria)

- Video compression standard ITU.T Rec. H.264 | ISO/IEC 14496-10 AVC.

- EXTREME SPEED, providing a constant throughput of >5 pixels encoded per clock cycle.

-

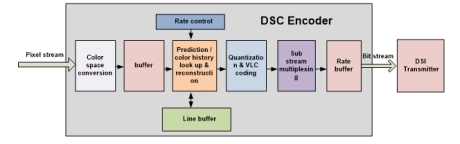

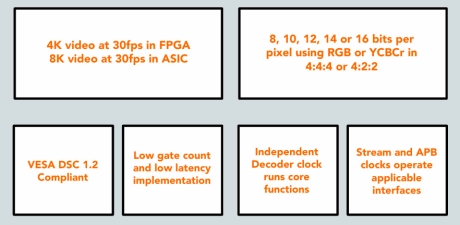

VESA DSC V1.2 Encoder

- VESA introduced the first Display Stream Compression (DSC) standard in 2014. The DSC 1.1 has been incorporated into the VESA Embedded DisplayPort (eDP) and MIPI® DSI embedded mobile interface standards. The latest VESA Display Compression-M (VDC-M) standard has also been adopted into the MIPI DSI standard. For mobile applications, DSC 1.1 and VDC-M mainly serve to reduce the video interface data rate, which reduces system power, prolongs battery life, and reduces interconnects to enable sleeker designs. For external display interfaces, DSC 1.2b extends resolution across existing connectors and cables, enabling 8K video and legacy support from the same connection.

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB. It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

- Programmable display resolutions

-

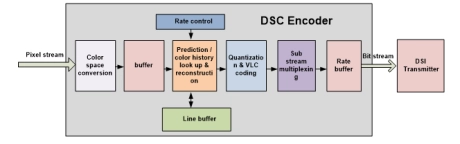

VESA DSC V1.2 Encoder

- Being compliant with the VESA DSC 1.2a and 1.2b standards, the IP core supports various prediction schemes (MMAP, BP, MPP, ICH) as well as color formats in YCbCr and RGB.

- It transfers more pixel data over display links to save memory size in embedded frame buffers in display driver ICs and performs visually lossless compression, low gate count and latency for ultra-high-definition display applications. It can be easily integrated into ASIC and FPGA applications.

-

H.265/HEVC 422 10bit Decoder for 4K

- Video stream

- - Compliant with ITU-T H.265, ISO/IEC 23008-2

- - Main / Main 12 Profile Level 1 to 6.1

- - Input format: Annex. B

-

Display Stream Compression (DSC 1.2) Encoder

- The Display Stream Compression (DSC) Encoder offers real-time compression of high-definition streams with resolutions up to 8K.

- The core supports 8, 10, 12, 14 or 16 bits per pixel input using either RGB or YCbCr in 4:4:4 or 4:2:2 format.

- The DSC Encoder core integrates industry standard interfaces for host configuration and control, video input, and output.

-

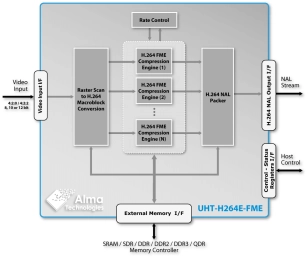

Scalable Ultra-High Throughput H.264 Encoder − Full Motion Estimation

- The UHT-H264E-FME core is a scalable, ultra-high throughput, hardware H.264 encoder, designed to enable 4K and 8K Ultra HD resolutions in power- and cost-effective FPGA or ASIC implementations.

- Powered by a highly-featured Full Motion Estimation engine, this encoder is the most advanced one of our UHT H.264 IP cores and offers best-in-class compression for applications needing advanced H.264 efficiency for high-quality, low-bitrate video encoding.

-

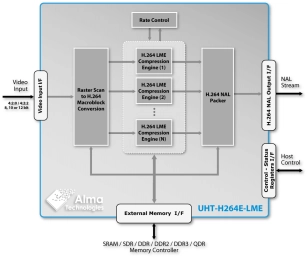

Scalable Ultra-High Throughput H.264 Encoder − Light Motion Estimation

- The UHT-H264E-LME core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.

-

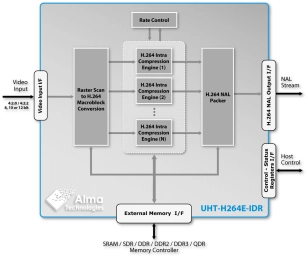

Scalable Ultra-High Throughput H.264 Encoder − Intra Frames (IDR) Encoding

- The UHT-H264E-IDR core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.