400G/800G Ethernet IP

Filter

Compare

12

IP

from

2

vendors

(1

-

10)

-

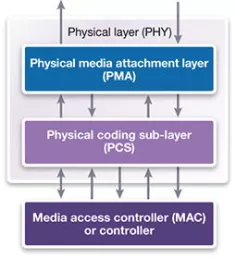

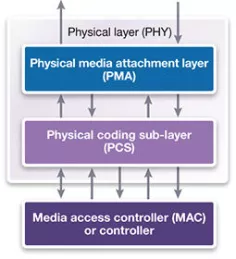

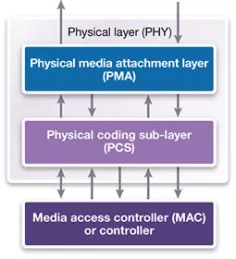

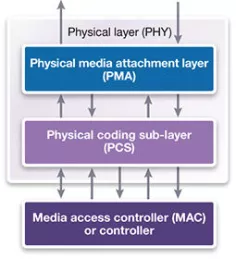

400G/800G High Speed Ethernet Controller PCS/FEC

- IEEE 802.3 compliant, UNH tested and ISO 26262 ASIL-B qualified

- Enhanced active functional safety features

-

400G/800G High Speed Ethernet Controller MAC/PCS/FEC

- Compliant with IEEE 802.3 and Ethernet Technology Consortium specifications

- Integrated FEC support including RS (528,514), RS(544,514), Firecode, Ethernet Technology Consortium Low Latency RS FEC

- Supports 802.3 PAUSE and 802.10bb Priority Flow Control (PFC) frame-based flow control, 802.3br Interspersing Express Traffic (IET) and IEEE 802.1AS Precision Time Protocol (PTP)

- APB interface for management and control

-

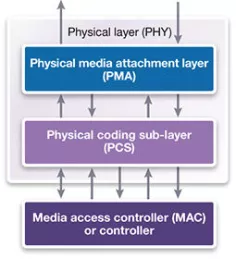

112G LR-Max Ethernet PHY for TSMC N5

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

-

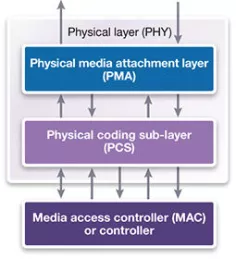

112G PHY G2, TSMC N5 x4, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

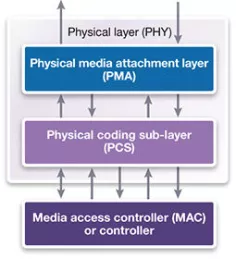

112G LRM PHY STD, TSMC N4P x4, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

112G VSR PHY, TSMC N3P x2, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

112G PHY, TSMC N3P x4 1.2V, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

112G LRM PHY, TSMC N3P x4, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

112G VSR PHY, TSMC N5 x8, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe

-

112G PHY, TSMC N5 x2, North/South (vertical) poly orientation

- Supports 1.25 to 112 Gbps data-rate

- Supports PCI Express 6.0, 1G to 400G/800G Ethernet, CCIX, CXL, JESD204C, CPRI, SATA, and OIF CEI LR/MR/VSR Electrical Interfaces protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC) support for PCIe