40 Gbps TCP Endpoint IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

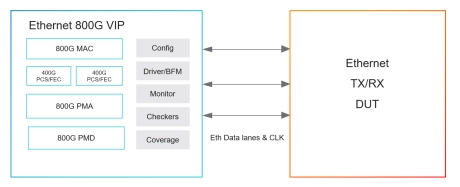

Simulation VIP for Ethernet up to 800G

- 800Gbps Interfaces

- 800Gbps Ethernet interfaces based on Ethernet Technology Consortium supports:

- 800GMII

- 800GBase-R Dual-PCS 32 lanes (25Gb/s)