32-bit DSP IP

Filter

Compare

112

IP

from

22

vendors

(1

-

10)

-

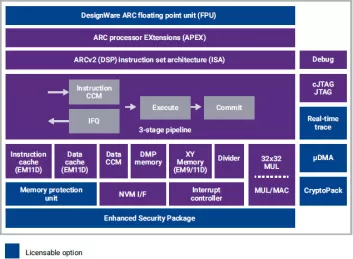

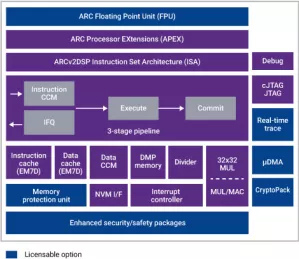

ARC EM9D 32-bit DSP Enhanced Processor core based on the ARCv2DSP ISA with CCM and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

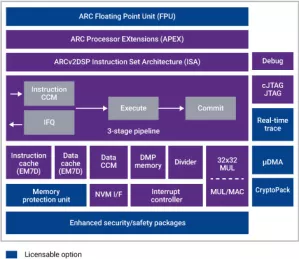

ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

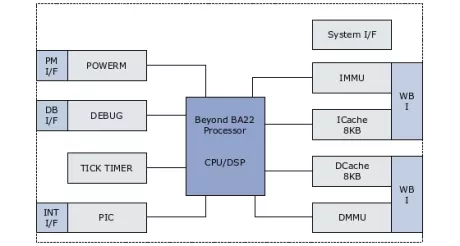

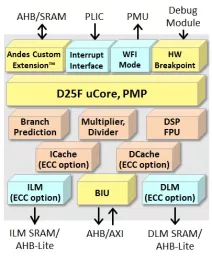

Highest code density, Low Power 32-bit Processor with optional DSP

- High Performance 32-bit CPU/DSP

- Power Management Unit

- Advanced Debug Unit

- Integrated Tick Timer

-

Compact High-Speed 32-bit CPU Core with DSP

- AndeStar™ V5 ISA, compliant to RISC-V technology

- DSP/SIMD ISA to boost the performance of digital signal processing

-

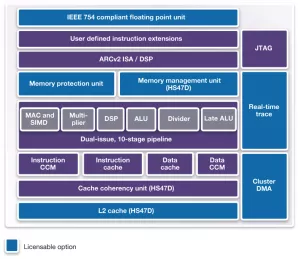

ARC HS47D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

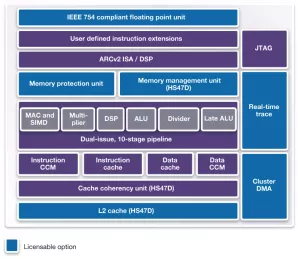

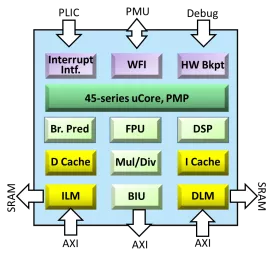

ARC HS45D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions for embedded applications

- Combination Dual-issue, 32-bit RISC + DSP processor

- Delivers up to 5700 DMIPS and 9880 CoreMark per core at 1.9 GHz on 16ff (worst case conditions, single-core configuration)

- ARCv2DSP ISA adds over 150 DSP instructions

- Easy DSP programming support with Metaware C/C++ Compiler

-

ARC EM5D Enhanced 32-bit processor core, ARCv2DSP ISA, for low power embedded DSP applications

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- The 32-bit D45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, “B” bit manipulation, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

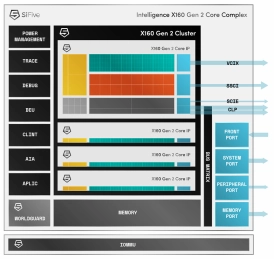

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

32-Bit Automotive Processor - 9-Stage Pipeline, Dual-issue

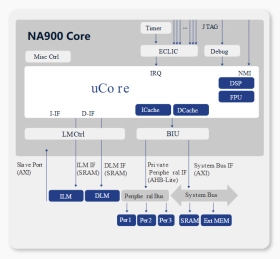

- NA900 series processor is the 1st ISO26262 ASIL-B/D Product Certified RISC-V CPU IP, Nuclei self-developed STL supports multiple ASIL-B automotive use cases.