32-Bit CPU IP

Filter

Compare

232

IP

from

43

vendors

(1

-

10)

-

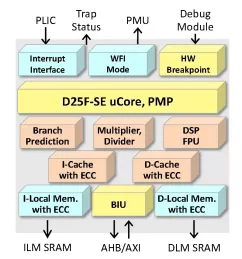

32-bit CPU IP core - ISO 26262 Automotive Functional Safety Compliant

- 32-bit CPU IP core that supports ISO 26262 ASIL B level functional safety for automotive applications

-

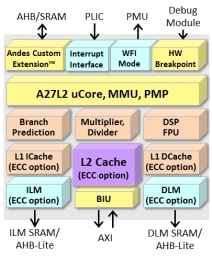

Compact High-Speed 32-bit CPU Core with Level-2 Cache

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- DSP/SIMD ISA to boost the performance of voice, audio, image and signal processing

- Andes extensions, architected for performance and functionality enhancements

-

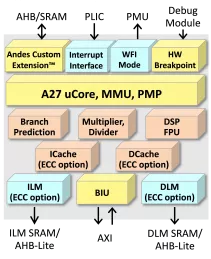

Compact High-Speed 32-bit CPU Core with MemBoost and PMA

- The 32-bit A27 is a 5-stage processor that supports the latest RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, “N” for user-level interrupts, and Memory Management Unit (MMU) for Linux support.

- A27 features branch prediction, instruction and data caches, local memories, ECC error protection, and Andes Custom Extension™ to add custom instructions to accelerate performance and reduce power consumption.

-

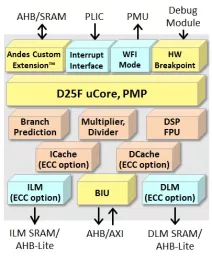

Compact High-Speed 32-bit CPU Core with DSP

- AndeStar™ V5 ISA, compliant to RISC-V technology

- DSP/SIMD ISA to boost the performance of digital signal processing

-

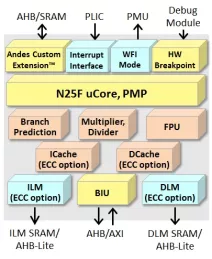

Compact High-Speed 32-bit CPU Core

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- Andes extensions, architected for performance and functionality enhancements

- Separately licensable Andes Custom Extension™ (ACE) for customized acceleration

-

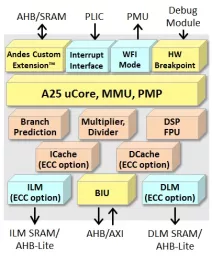

Compact High-Speed 32-bit CPU for Real-time and Linux Applications

- AndesCore™ A25 is a 32-bit CPU IP core based on AndeStar™ V5 architecture which incorporated RISC-V technology, it is capable of delivering high per-MHz performance and operating at high frequencies, at the same time it is small in gate count.

- A25 also supports the RISC-V P-extension (draft) DSP/SIMD ISA contributed by Andes, single- and double-precision floating point and bit-manipulation instructions, and MMU for Linux based applications.

-

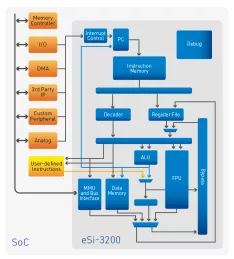

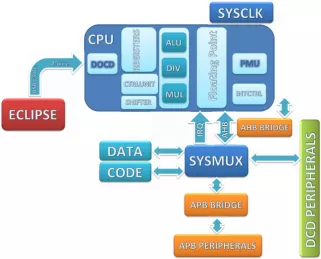

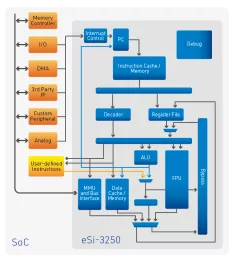

Scalable & Royalty-Free 32-bit CPU

- Configurable 32-bit Harvard architecture

- Performance up to 1.48 / 2.67 DMIPS/MHz and 2.41 CoreMarks/MHz

- Small footprint starting at 10.6k/6.8k ASIC gates

-

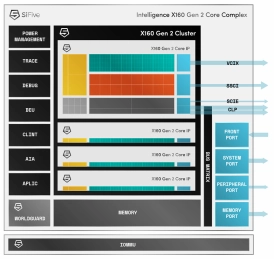

Multi-core capable 32-bit RISC-V CPU with vector extensions

- The SiFive® Intelligence™ X160 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge.

- With this 32-bit version, X100 series IP can be optimized for power efficiency and severely area-constrained applications.

-

High-performance 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

-

Compact, low-power 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

- Optional IEEE 754 floating point unit (FPU)