2D/2.5D Graphics Engine IP

Filter

Compare

55

IP

from

18

vendors

(1

-

10)

-

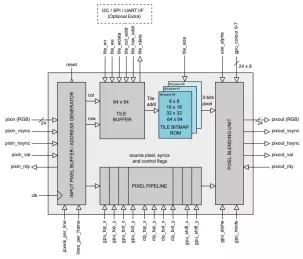

Graphics Processor Overlay IP Core

- Technology independent soft IP Core for FPGA, ASIC and SoC devices

- Supplied as human-readable VHDL (or Verilog) source code

-

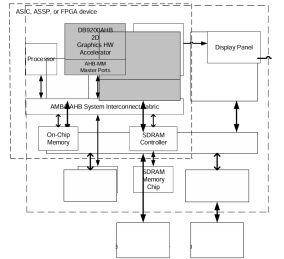

2D Graphics Hardware Accelerator (AHB Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

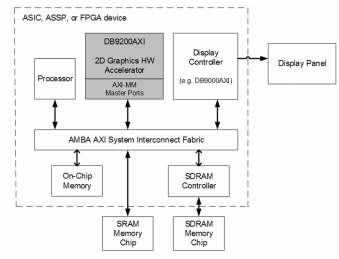

2D Graphics Hardware Accelerator (AXI Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

Fourth-generation Valhall-based graphics processing unit (GPU) for premium mobile market

- Variable Rate Shading for Performance and Energy Boost

- Evolving Execution Engine for Greater Compute Power

- Massive ML Uplift for Advanced Intelligence

-

Third-Generation Valhall-based Graphics Processing Unit (GPU) for the sub-premium market

- Redesigned Execution Engine for Lower-Cost Gaming

- Improved Quality for Smartphone Market Growth

- Industry-Leading Battery Efficiency

-

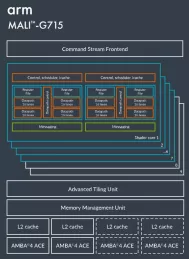

Third-Generation Valhall-based Graphics Processing Unit (GPU) for Premium Market

- Command Stream Frontend for Advanced Gaming

- Large Cores Provide Highest-Ever Energy Efficiency

- ML Uplift Brings More Advanced Experiences to Mobile

-

2D Blit and Raster Graphics

- All buffer formats 100% compatible

- Flexible pixel formats (1/2/4/8/16/18/24/32 bpp; any bit width per channel)

- YUV support (packed, planar, 4:4:4, 4:2:2, 4:2:0, progressive, interlaced)

- Dynamic re-configuration of processing units

-

Advanced 2D Graphics Controller

- Fully synchronous, synthesizable and technology independent RTL code

- Capable of drawing shapes such as pixels, lines and rectangles

-

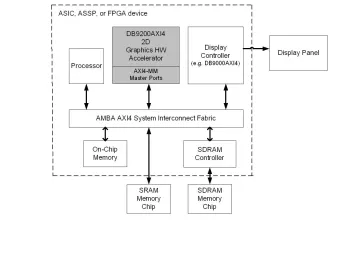

2D Graphics Hardware Accelerator (AXI4 Bus)

- Generates bitmaps from graphics instructions as well as combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT) which lay the foundation for power hardware graphics primitive operations

- Generates characters from compressed bitmaps using its FONT Bitmap Color Expansion Unit

- Performs Alpha Blend operations of bitmaps with its Alpha Blend unit

- Draws lines, polygons, circles using its hardware efficient & pixel accurate Bresenham Algorithm Line Drawing Unit

-

2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- Pixel performance

- 3D rendering

- Texture size

- 2D rendering