25G Ethernet IP

Filter

Compare

80

IP

from

17

vendors

(1

-

10)

-

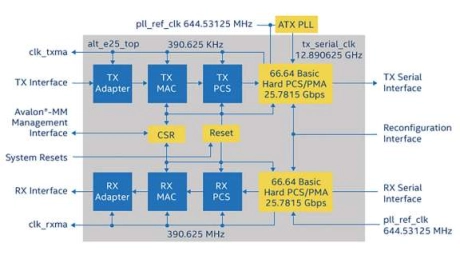

25G Ethernet Intel® FPGA IP

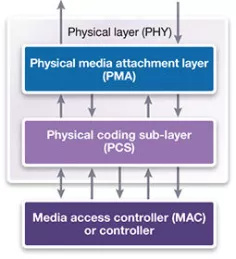

- This IP core implements the 25G and 50G Ethernet Specification, Draft 1.4 from the 25 Gigabit Ethernet Consortium

- The IP core includes an option to support unidirectional transport as defined in Clause 66 of the IEEE 802.3-2012 Ethernet Standard. The media access control (MAC) client side interface for the 25GbE IP core is a 64 bit Avalon® streaming interface (Avalon-ST)

- It maps to one 25.78125 Gbps transceiver

- The IP core optionally includes Reed-Solomon forward error correction (FEC) for support of direct attach copper (DAC) cable.

-

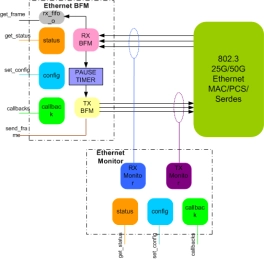

Ethernet 25G,50G Verification IP

- Supports 25G and 50G Speeds as per the 802.3-2018 specification,

- 25GBase_R

- 25GBase_KR

- 50GBase_KR

-

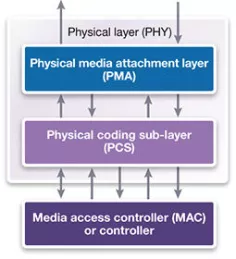

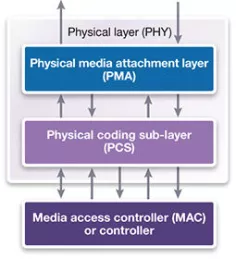

25G Ethernet PHY in TSMC (16nm, 12nm, N7)

- Includes one, two or four full-duplex transceivers (transmit and receive functions)

- Supports back channel initialization, aggregation, bifurcation, and power management

- Supports both internal and external reference clock connections to the PHY

- Configurable transmitter and receiver equalization, supporting chip-to-chip, port side, backplane interfaces

-

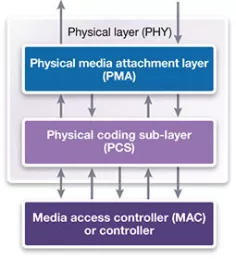

25G Ethernet PHY in GF (14nm)

- Includes one, two or four full-duplex transceivers (transmit and receive functions)

- Supports back channel initialization, aggregation, bifurcation, and power management

- Supports both internal and external reference clock connections to the PHY

- Configurable transmitter and receiver equalization, supporting chip-to-chip, port side, backplane interfaces

-

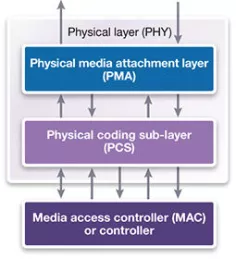

25G MR Ethernet PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

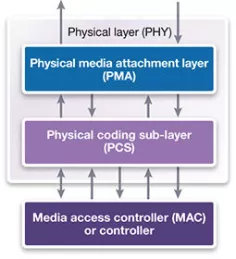

25G MR Ethernet PHY, TSMC 16FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 16FFC x1 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 12FFC x8 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 12FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features