1G Ethernet PHY IP

Filter

Compare

221

IP

from

13

vendors

(1

-

10)

-

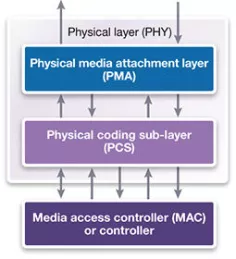

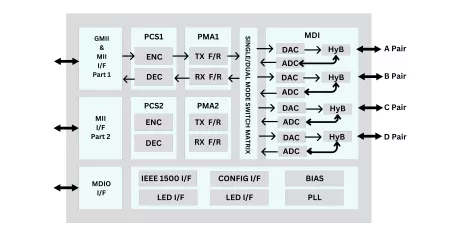

Silicon Proven 1G Ethernet PHY IP as Whitebox

- IEEE 802.3-2008, IEEE 802.3az fully standards compliant

- IEEE 1588-2008 support

- BroadR-Reach™ support

- Dual port MAC interface:

-

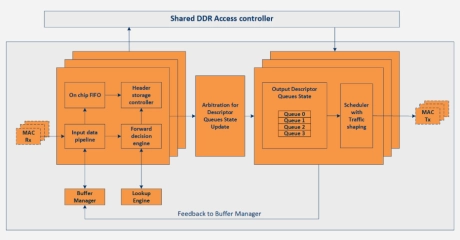

Deep Buffering Memory 1G Ethernet Switch

- The 1G deep buffering memory Ethernet Switch is an advanced Ethernet switching IP that supports buffering large amounts of data in external RAM.

- The non-blocking Ethernet switch IP core enables fine-grained traffic differentiation for rich implementations of packet prioritization, enabling per port and per queue shaping on egress ports.

-

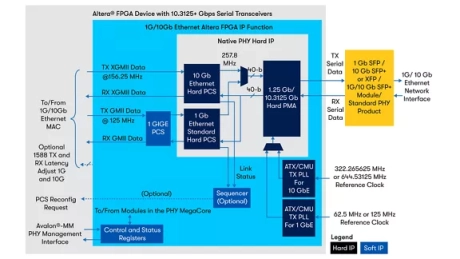

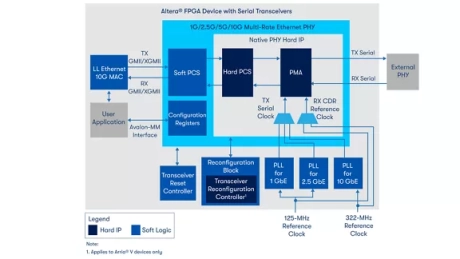

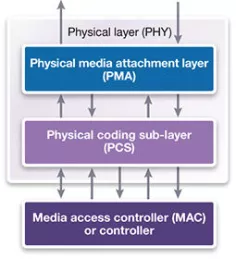

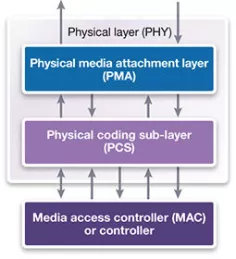

1G/10Gb Ethernet PHY Intel® FPGA IP

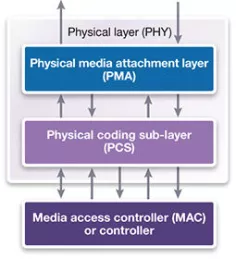

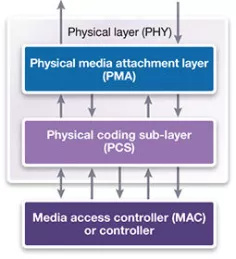

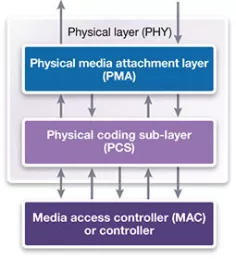

- The 1G/10G Ethernet PHY Intel® FPGA Intellectual Property (IP) core supports functionality of both the standard physical coding sublayer (PCS) and the higher data rate 10G PCS with an appropriate physical medium attachment (PMA)

- The Standard PCS implements the 1GbE protocol as defined in Clause 36 of the IEEE 802.3 2005 Standard and also supports auto-negotiation as defined in Clause 37 of the IEEE 802.3 2005 Standard

- The 10G PCS implements the 10G Ethernet protocol as defined in the IEEE 802.3 2005 standard.

-

Multi-Rate Ethernet PHY FPGA IP

- The Multi-Rate Ethernet PHY FPGA IP core can dynamically support multiple data rates without any design regeneration or device reconfiguration

- This IP allows the creation of a 1G to 10G configuration that allows dynamic reconfiguration across all Ethernet rates from 10M, 100M, 1G, 2.5G, 5G, and 10G.

-

25G MR Ethernet PHY, TSMC 7FF x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 7FF x2 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 16FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 16FFC x1 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 12FFC x8 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features

-

25G MR Ethernet PHY, TSMC 12FFC x4 North/South (vertical) poly orientation

- Supports 1.25 to 25.8 Gbps data-rate

- Supports PCI Express 4.0 with lane margining, 1G to 100G Ethernet, CCIX, and SATA protocols

- Supports x1 to x16 macro configurations with aggregation and bifurcation

- Spread Spectrum Clock (SSC), ` PCIe Separate Refclk Independent SSC (SRIS) and power management features