100 Gigabit Ethernet IP

Filter

Compare

17

IP

from

12

vendors

(1

-

10)

-

Gigabit Ethernet Media Access

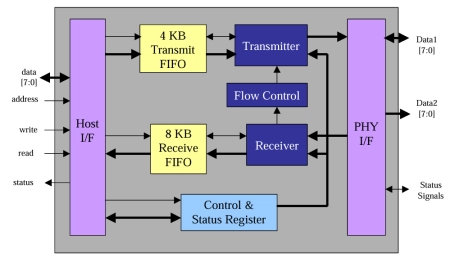

- The GEMAC (Gigabit Ethernet Media Access Controller) core implements the Ethernet Media Access Control (MAC) protocol according to IEEE 802.3 specification.

- The MAC has a standard Gigabit Media Independent Interface (GMII) to connect to any PHY interface.

- The core can be used in various integrated applications. A single channel MAC with PCI controller would provide an ideal solution for inexpensive NIC cards.

-

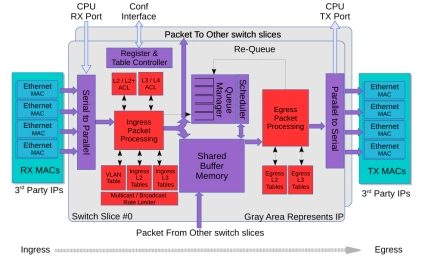

Ethernet Switch/Router Datacenter ToR 32x100G

- 32 x 100 Gigabit Ethernet ports.

- Full wire-speed on all ports and all Ethernet frame sizes.

- Store and forward shared memory architecture.

- Support for jumbo packets up to 32738 bytes.

-

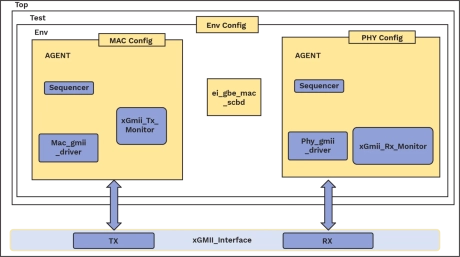

100G Ethernet Verification IP

- The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems.

- Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards.

- Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.

-

Ethernet Device Driver

- The 802.3 Ethernet Device Driver is developed to support both the 10/ 100 Ethernet IP as well as its Gigabit Ethernet IP.

- The device driver provides communications between the MAC (Medium Access Control) and the OS (Operating System) as well as access to the overlying network layer protocol and the applications layer.

-

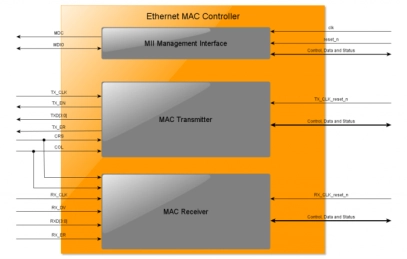

10/100/1000 Ethernet MAC DO-254 IP Core

- The 10/100/1000 Ethernet MAC Controller DO-254 IP Core implements the Media Access Control as specified in the IEEE 802.3-2008 specification.

- The Ethernet MAC Controller has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit.

-

Flexibilis Redundant Switch - 3 to 8 Port Ethernet IP with HSR/PRP

- Provides seamless redundant communication for critical traffic

- Open, interoperable solution supporting HSR, PRP and IEEE 1588 PTP standards

-

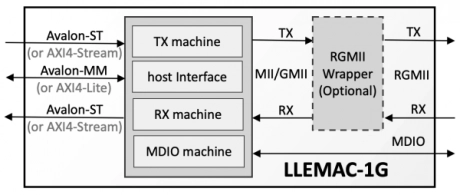

Low-Latency 10/100/1000 Ethernet MAC

- The LLEMAC-1G implements an Ethernet Media Access Controller (MAC) compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

-

UltraScale+ Integrated 100G Ethernet Subsystem

- Optional built-in 100G RS-FEC

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- Requires license key available at no charge

- 1588 1-step and 2-step hardware time stamping

-

UltraScale Integrated 100G Ethernet Subsystem

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- No charge 100G Ethernet MAC and PCS license key enabled

- Optional fee based soft 100G RS-FEC for UltraScale FPGAs

- 1588 1-step and 2-step hardware time stamping

-

UltraScale Integrated 100G Ethernet MAC/PCS

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- No charge license key enabled

- 1588 1-step and 2-step hardware time stamping

- Allows insertion of custom logic such as RS-FEC between the 100G Ethernet integrated block and GT