Interface IP Cores

Interface IP cores are used to achieve communication between chips and external devices or other chips. Common interface standards include USB, PCIe, SATA, I2C, SPI, Ethernet, etc.

Explore our vast directory of Interface IP cores below.

All offers in

Interface IP Cores

Filter

Compare

3,553

Interface IP Cores

from 177 vendors

(1

-

10)

-

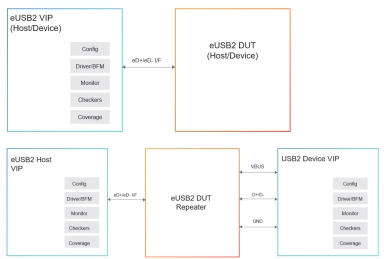

Simulation VIP for eUSB

- Supported DUT Types

- All eUSB DUT types such as in native mode: Host(eDSPn) or Device(eUSPn), in Repeater Mode: Host(eDSPr) or Device(eUSPr), Host Repeater, Peripheral Repeater and Hybrid Repeater.

- Transaction Types

- All types of transfers: bulk, control, interrupt, and isochronous transactions

-

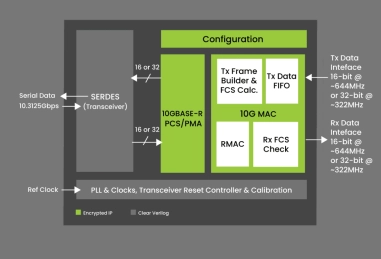

10-Gbps Ultra-Low Latency Ethernet MAC and PCS

- The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances.

- The 10G IP core support both 16b (644MHz) and 32b (322MHz) modes, and can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic with no dropped packets.

-

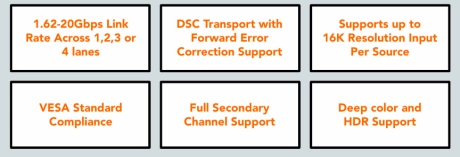

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes

-

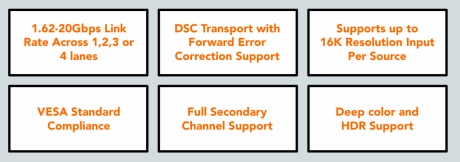

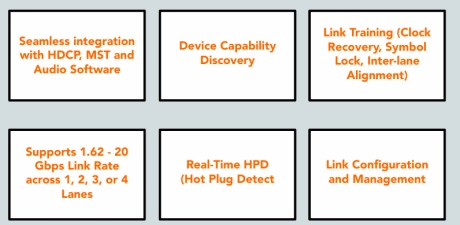

DisplayPort Transmitter IP

- Our 6th generation DisplayPort Transmitter Link Controller core supports DisplayPort 2.1, DisplayPort 1.4a and embedded DisplayPort 1.5.

- Features include link rates up to 20Gbps for DisplayPort 2.0, 8.1Gbps for DisplayPort 1.4a. Display Steam Compression (DSC), multi-stream transport (MST) and more. The base core includes all required link functionality— Main Link, Secondary Channel, and AUX Channel protocols—and supports the HDCP 2.3 standards for data encryption.

-

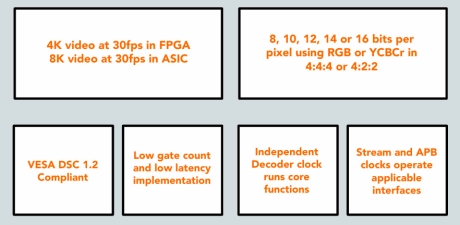

Display Stream Compression (DSC 1.2) Encoder

- The Display Stream Compression (DSC) Encoder offers real-time compression of high-definition streams with resolutions up to 8K.

- The core supports 8, 10, 12, 14 or 16 bits per pixel input using either RGB or YCbCr in 4:4:4 or 4:2:2 format.

- The DSC Encoder core integrates industry standard interfaces for host configuration and control, video input, and output.

-

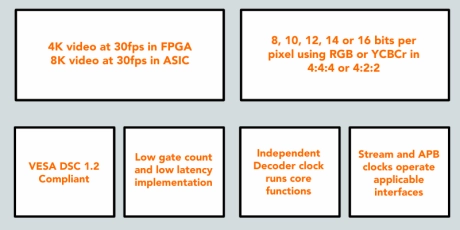

Display Stream Compression (DSC 1.2) Decoder

- The Display Stream Compression (DSC) Decoder core offers realtime decompression of high-definition streams with resolutions from 480 to 8K.

- The core supports 8, 10, 12, 14 or 16 bits per pixel using either RGB or YCbCr in 4:4:4 or 4:2:2 format.

- The DSC Decoder core integrates industry standard interfaces for host configuration and control, data input, and video output.

-

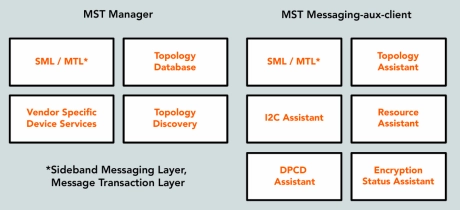

MST Topology Management Stack

- The DisplayPort Multi Stream Transport (MST) Topology Management Software implements MST topology management for multiple monitors on a Trilinear DisplayPort Transmitter IP core.

- The software enables customers to shorten time to market and reduce design risk using pre-tested, ready-to-deploy software.

-

DisplayPort Link Policy Maker

- The DisplayPort Link Policy Maker (LPM) is a DisplayPort 1.4/2.0 compliant software stack that manages and controls the DisplayPort serial link and AUX channel communications.

- The software provides for enumeration and configuration of the source and sink devices, adaptive training of the DisplayPort link, video stream allocation and transmission, AUX channel traffic management and handling of all HPD (Hot Plug Detect) events.

-

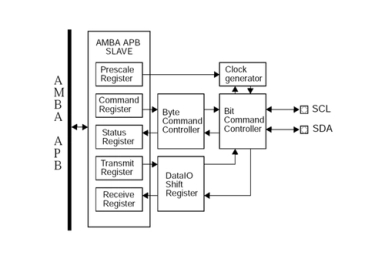

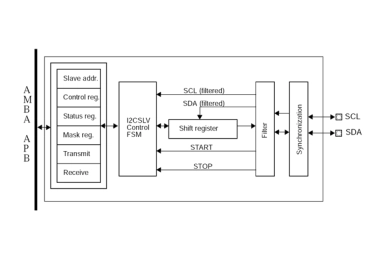

I²C Slave

- The I²C slave core is a simple I²C slave that provides a link between the I²C bus and the AMBA APB.

- The core is compatible with the Philips I²C standard and supports 7- and 10-bit addressing with an optionally software programmable address.

- Standard-mode (100 kb/s) and Fast-mode (400 kb/s) operation are supported directly.

-

I²C Master

- The I²C master core is a simple I²C master that provides a link between the I²C bus and the AMBA APB.

- The I²C-master core is a modified version of the OpenCores I²C-Master where the WISHBONE interface has been replaced with an AMBA APB interface.

- The core is compatible with Philips I²C standard and supports 7- and 10-bit addressing. Standard-mode (100 kb/s) and Fast-mode (400 kb/s) operation are supported directly.