USB 3.0 PHY IP

Welcome to the ultimate USB 3.0 PHY IP hub! Explore our vast directory of USB 3.0 PHY IP

All offers in

USB 3.0 PHY IP

Filter

Compare

122

USB 3.0 PHY IP

from

14

vendors

(1

-

10)

-

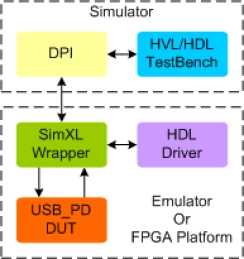

USB PD Synthesizable Transactor

- USB PD Features

- Supports USB Power Delivery Specification 3.1,3.0, 2.0 and 1.0

- Supports USB Type-C Cable and Connector Specification

- Supports Cable plug communication

-

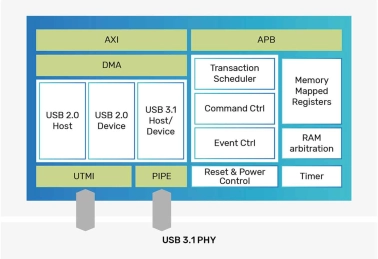

USB 3.x Controller

- Full Link Power Management (U0, U1, U2, and U3) with LFPS support

- Up to 15 IN and 15 OUT configurable endpoints

- Power and clock gating feature support

- Multi-channel Scatter/Gather DMA with TRB caching

- AXI features 128-bit datapath width and 64-bit address width

-

USB-C 3.0 femtoPHY, Type-C - TSMC 28HPC, North/South Poly Orientation

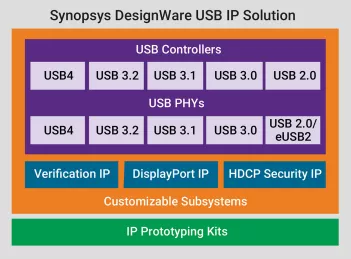

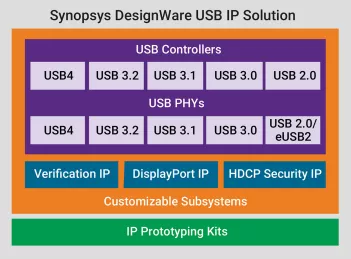

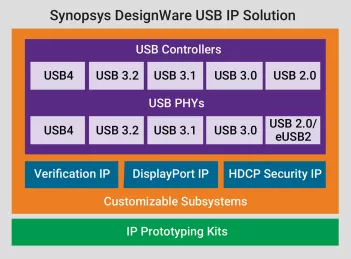

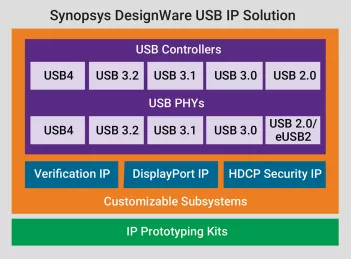

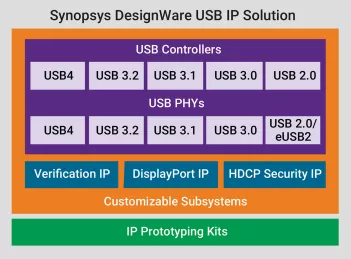

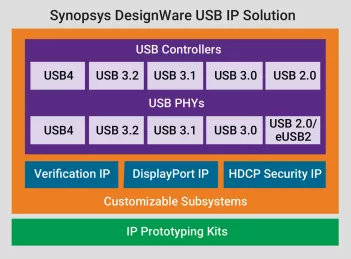

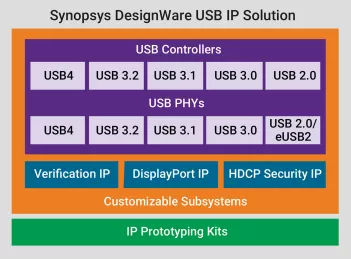

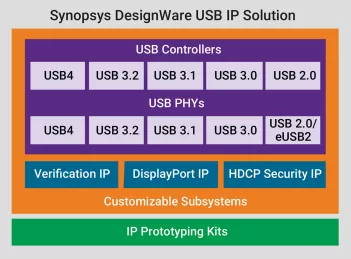

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB-C 3.0 femtoPHY, Type-C - TSMC 16FFC, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB-C 3.0 femtoPHY, Type-C - TSMC 16FF+LL, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB-C 3.0 femtoPHY, Type-C - TSMC 12FFC, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB 3.0 SSPHY, GF22FDSOI x1, North/South (vertical) poly orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB 3.0 SSPHY - UMC 65LL x1

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB 3.0 PHY-TSMC 28HPM18 x1 OTG, North/South Poly Orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification

-

USB 3.0 PHY-GF 28HPP18 x1 OTG, East/West poly orientation

- Part of a comprehensive IP solution including xHCI host and device controllers, PHYs, verification IP, IP Prototyping Kits and IP software development kits

- Designed for advanced 1.8V CMOS planar bulk and FinFET process nodes

- USB-C femtoPHY IP supports USB Type-C specification